Mixed-Signal Analog

Low-Current Readout

Low-Current Readout

NIST Nanotechnology Accelerator project.

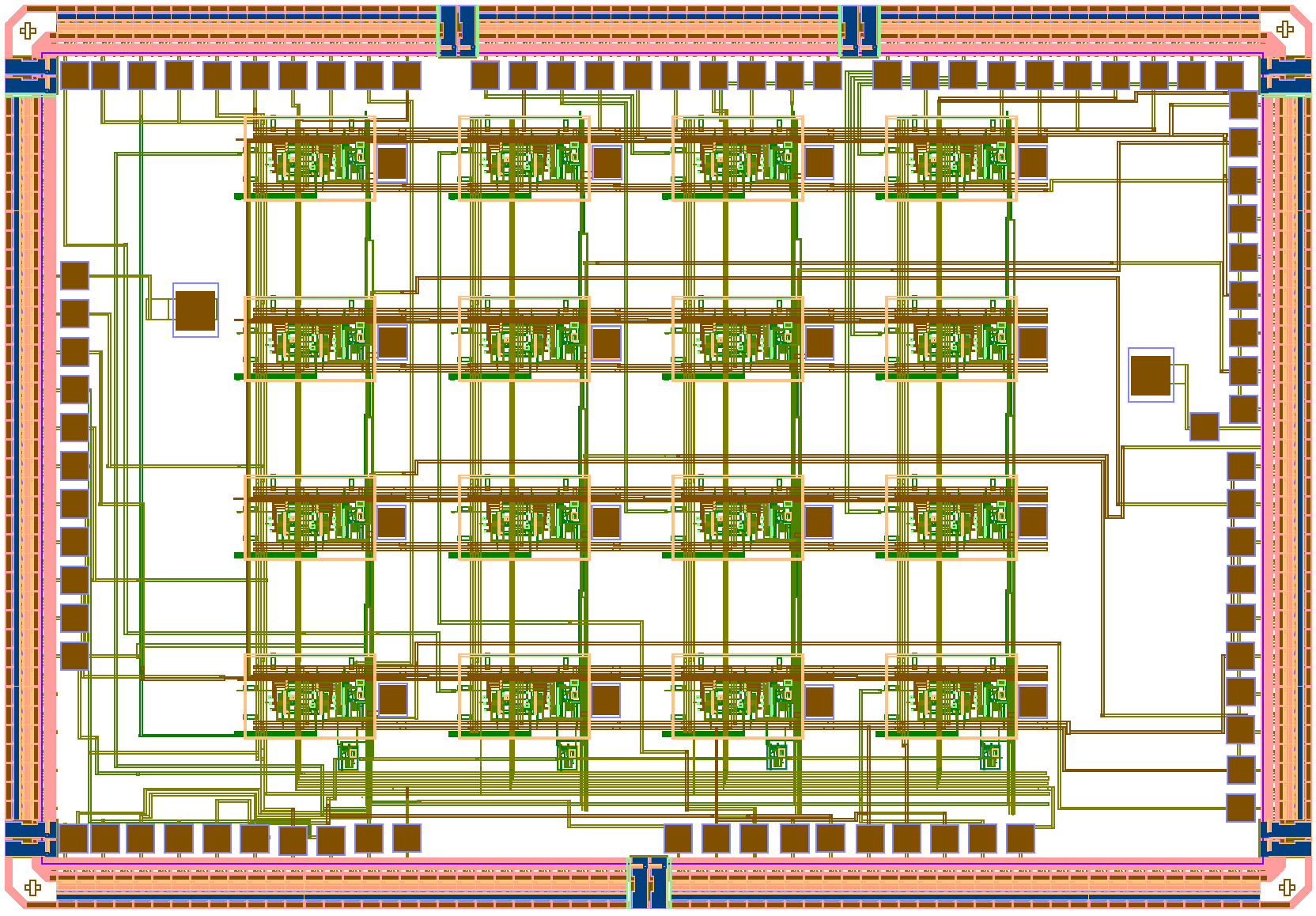

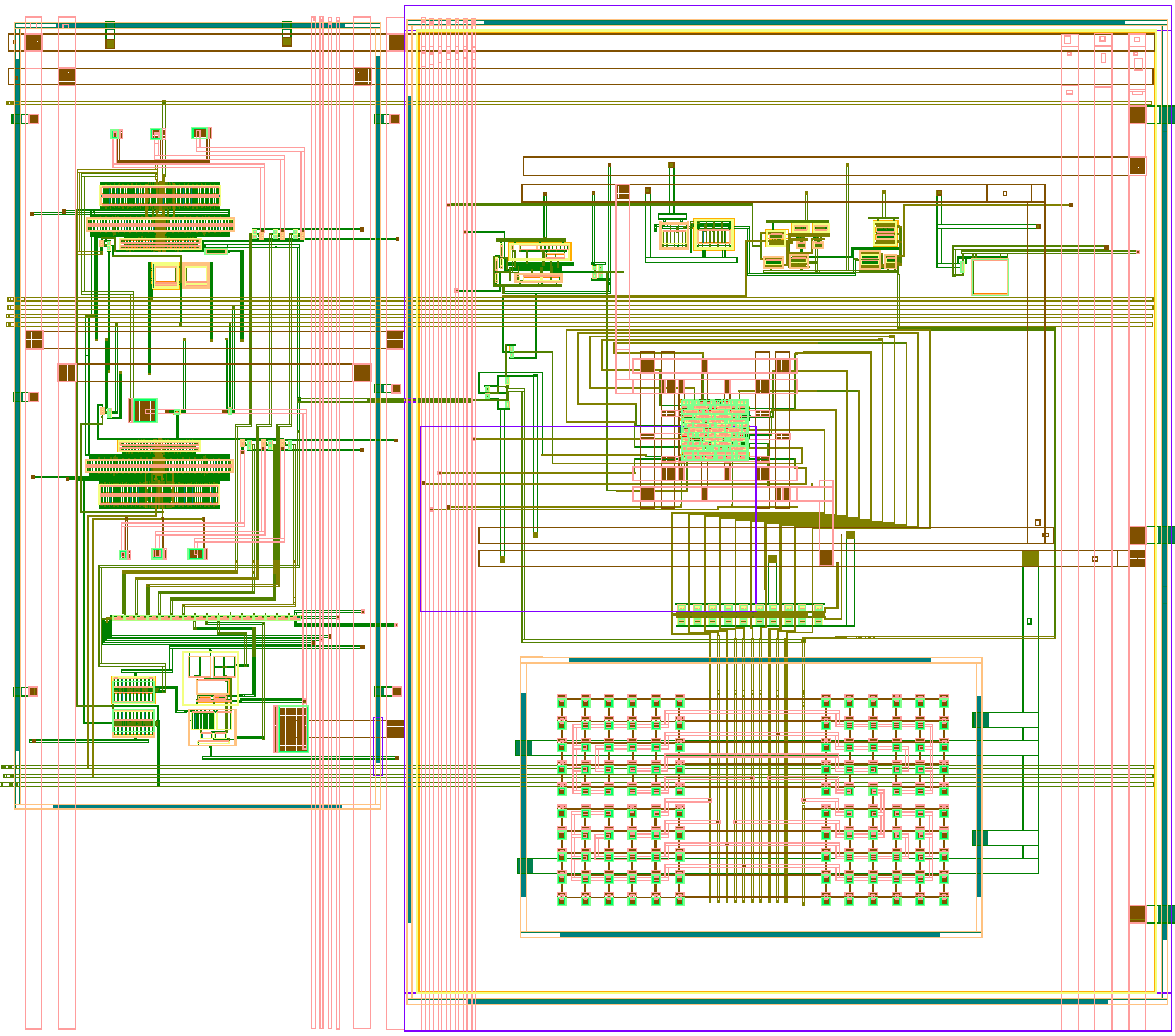

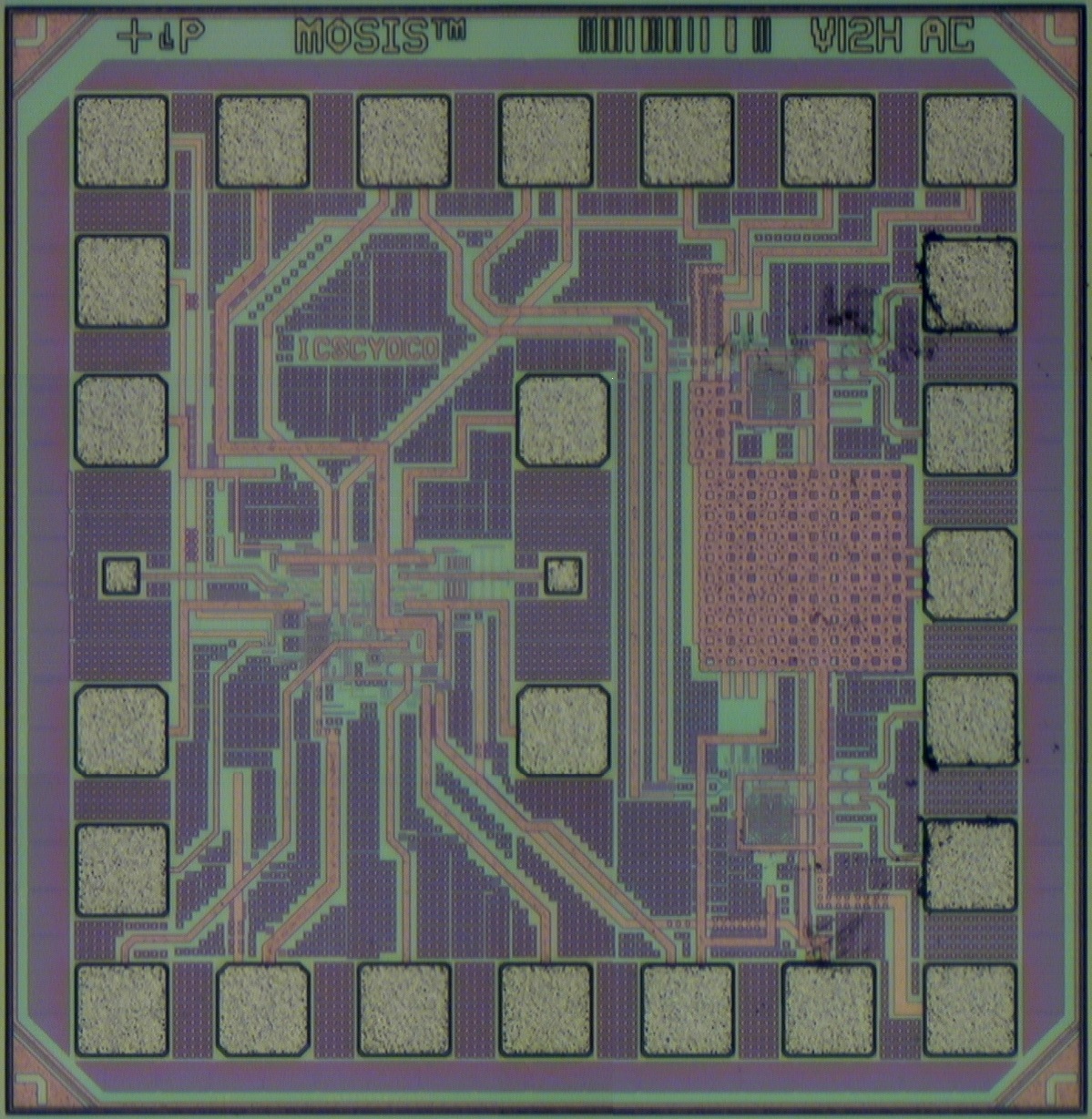

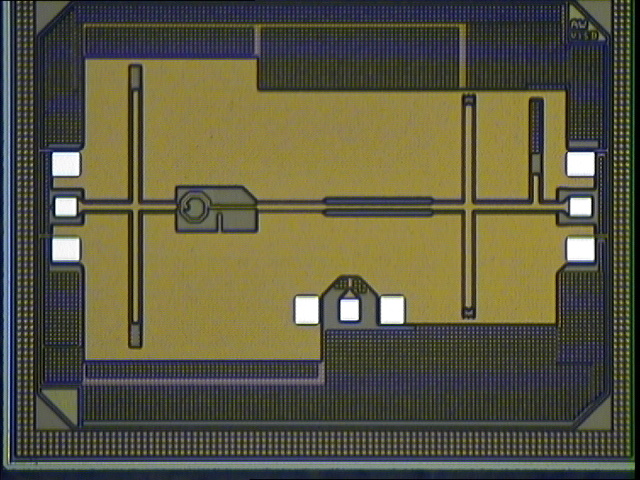

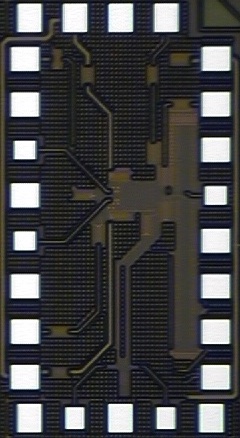

DNA-to-Digital Conversion Array (v3)

DNA-to-Digital Conversion Array (v3)

DNA molecules in / electronic bits out. Lots of analog & digital in between. 130-nm CMOS.

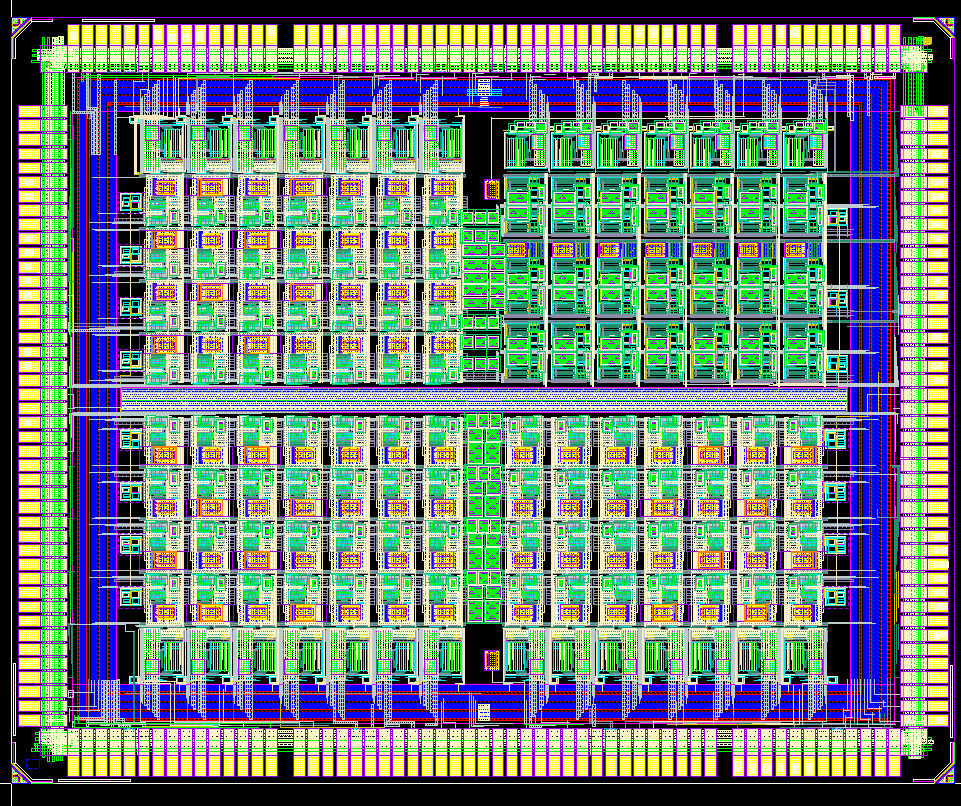

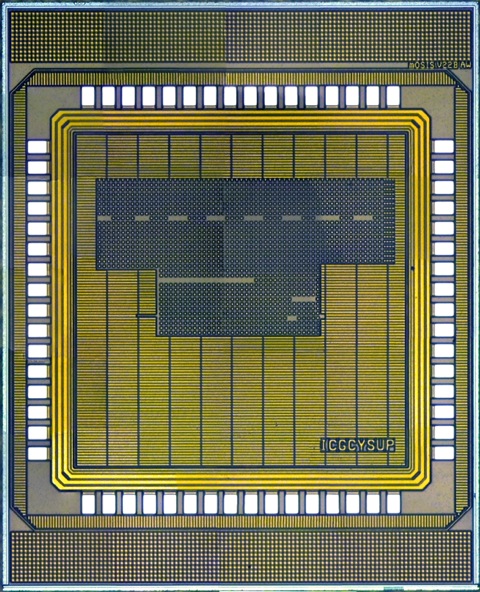

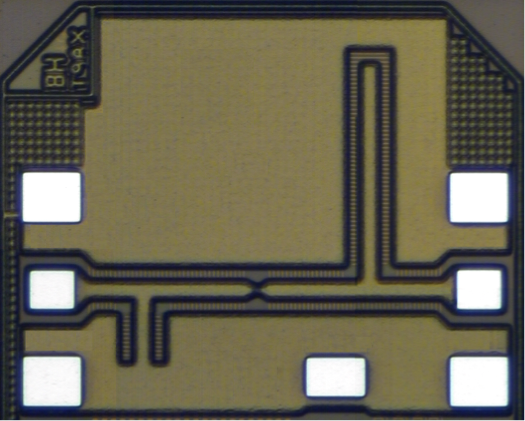

DNA-to-Digital Conversion Array (v2)

DNA-to-Digital Conversion Array (v2)

As above. But different timing scheme. 130-nm CMOS

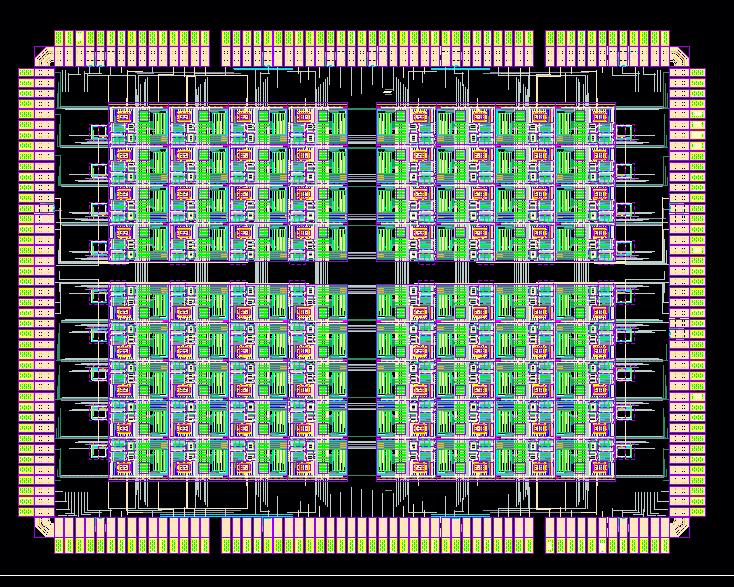

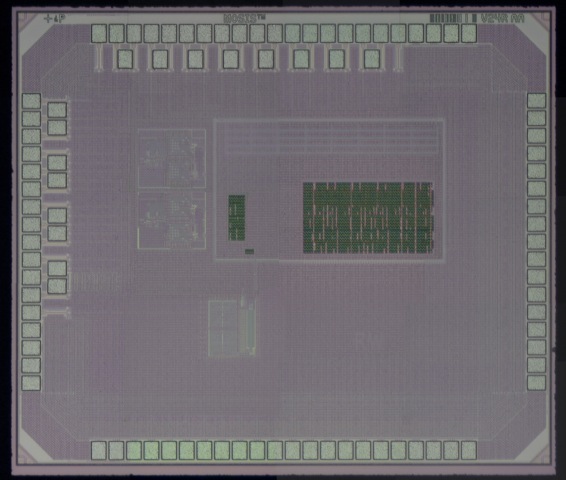

DNA-to-Digital Conversion Array

DNA-to-Digital Conversion Array

As above. Different circuitry. The granddaddy of 'em all. 130-nm CMOS.

Low-Noise Current Detector

Low-Noise Current Detector

Design for IEEE SSCS supported Chipathon project.

Embedded Processors

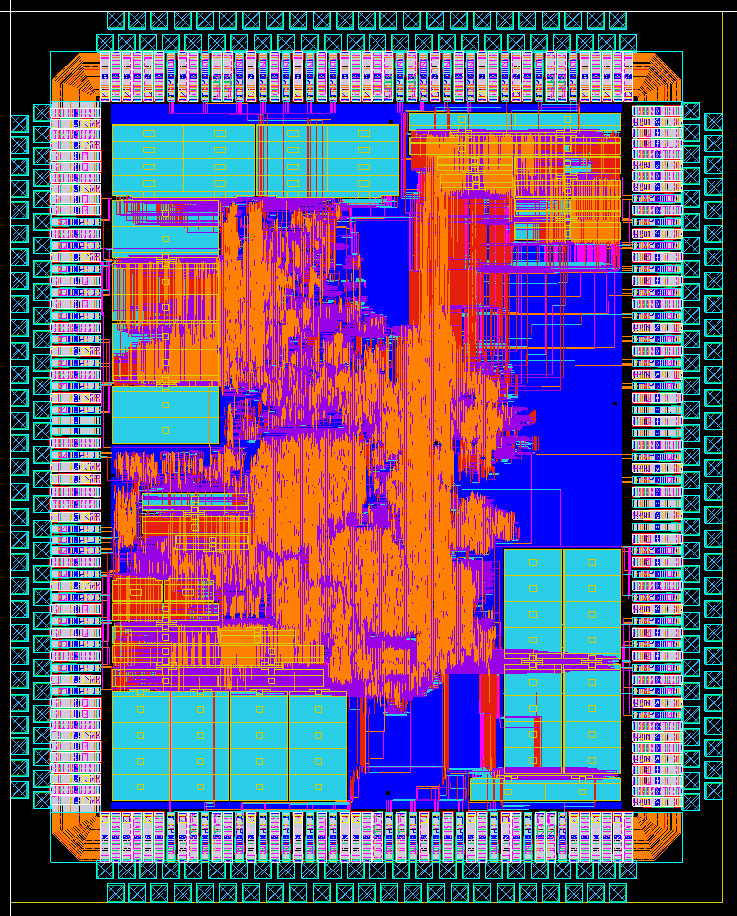

More Bigger RISC-V DNA Sequencer

More Bigger RISC-V DNA Sequencer

Beefier AI for DNA sequencing. 22-nm CMOS.

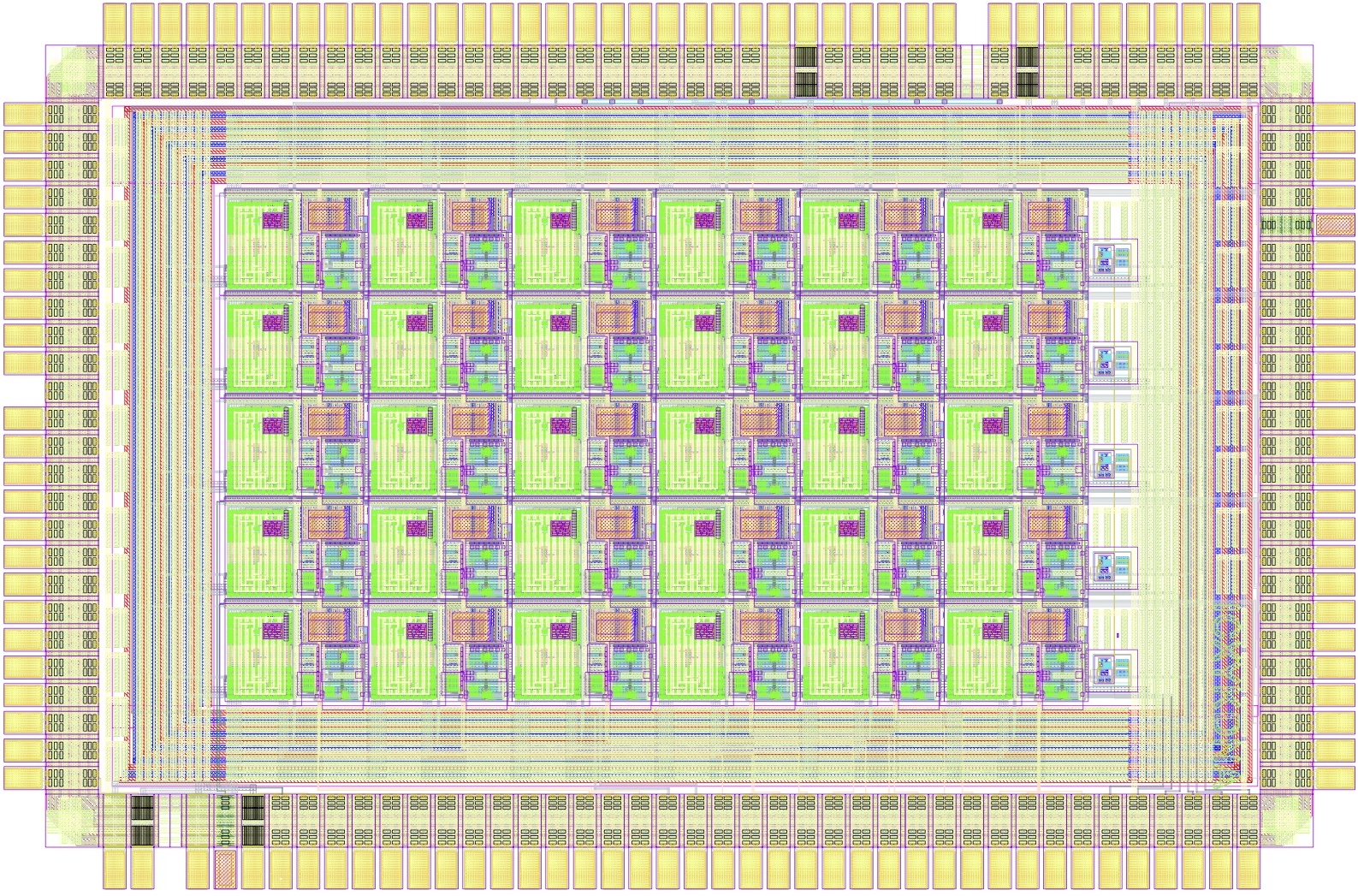

Multicore RISC-V DNA Sequencer

Multicore RISC-V DNA Sequencer

Deep-learning-enchanced bioinformatics (some analog iniside). 22-nm CMOS.

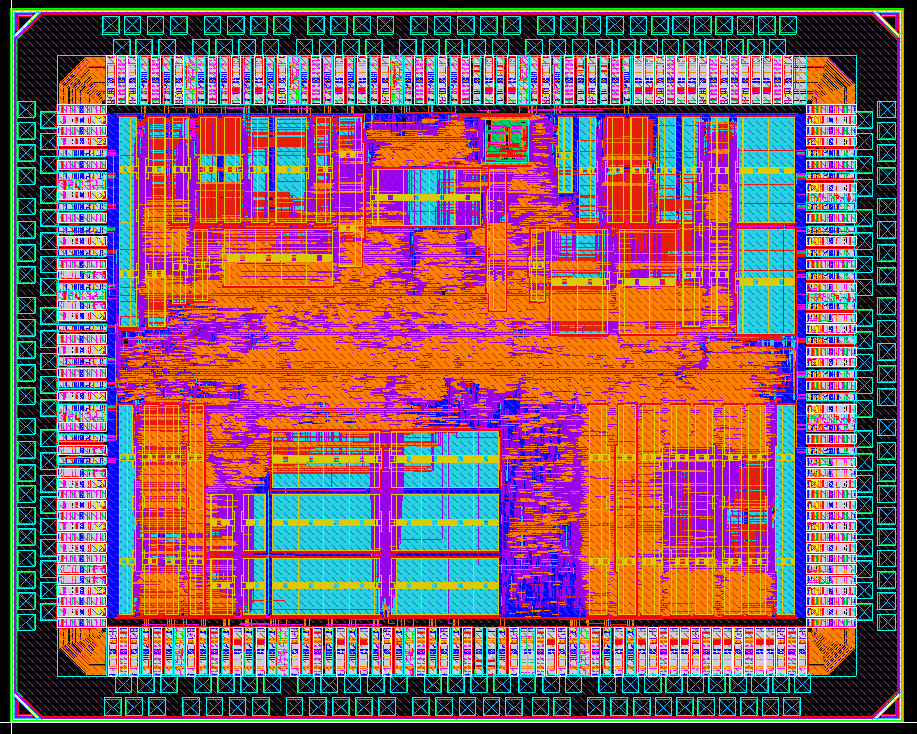

DNA Sequencer

DNA Sequencer

Electronic bits in / DNA basecalls out (e.g., ...CCGTTAAATTGG...). RISC-V + AI bioinformatics hardware acceleration in between. Linux capable. 22-nm CMOS.

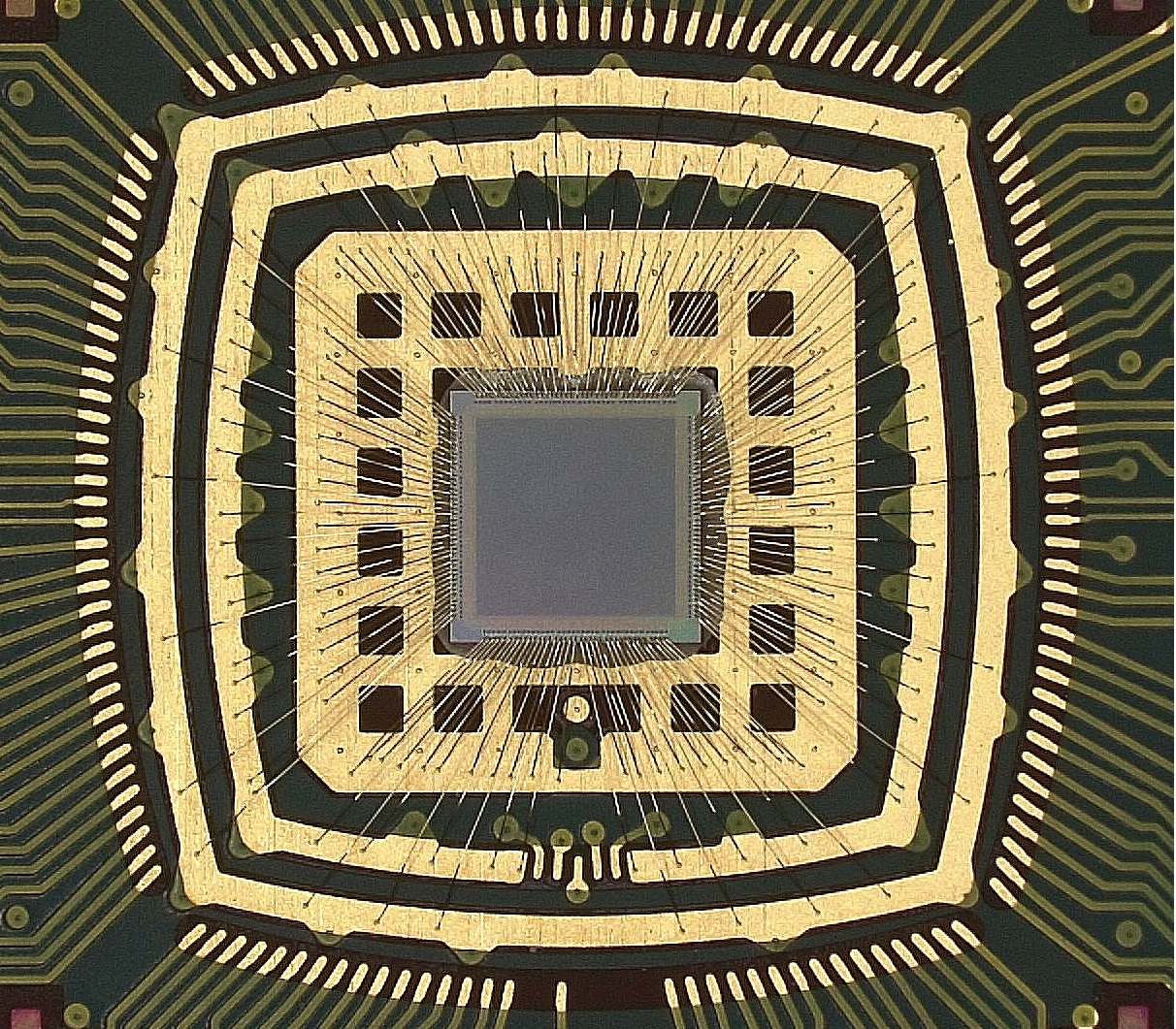

DNA Sequencer (bonded)

DNA Sequencer (bonded)

The above, just snug to its package frame.

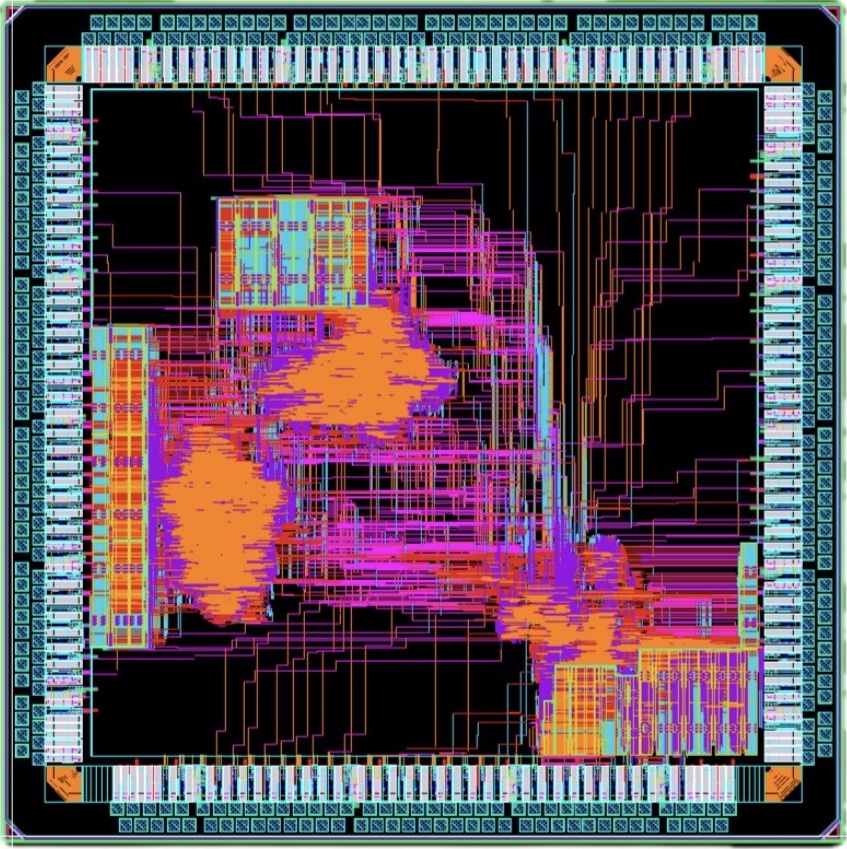

Mixed-Signal Nonlinear Path Planner

Mixed-Signal Nonlinear Path Planner

Robot brain. Same idea as below. Has data converters for sensors (ADCs) & actuators (DACs). 90-nm CMOS.

Nonlinear Path Planner

Nonlinear Path Planner

Micro-bot planner. Implements a nonlinear Lyapunov-based controller processor. Optimized for a trimmed down ISA (MIPS-based) to save power, but still allows algorithm to scale. Intended to operate in subthreshold. 130-nm CMOS.

RFIC/Wireless/Wireline

10-Gbps On-Chip Scope

10-Gbps On-Chip Scope

Fast sampling of clock and random data as expected in high-speed wireline comms. 65-nm CMOS.

100-GHz Parametric Tripler

100-GHz Parametric Tripler

3X frequency without the need for an idler (a good thing if you want to keep the cost down). 130-nm CMOS.

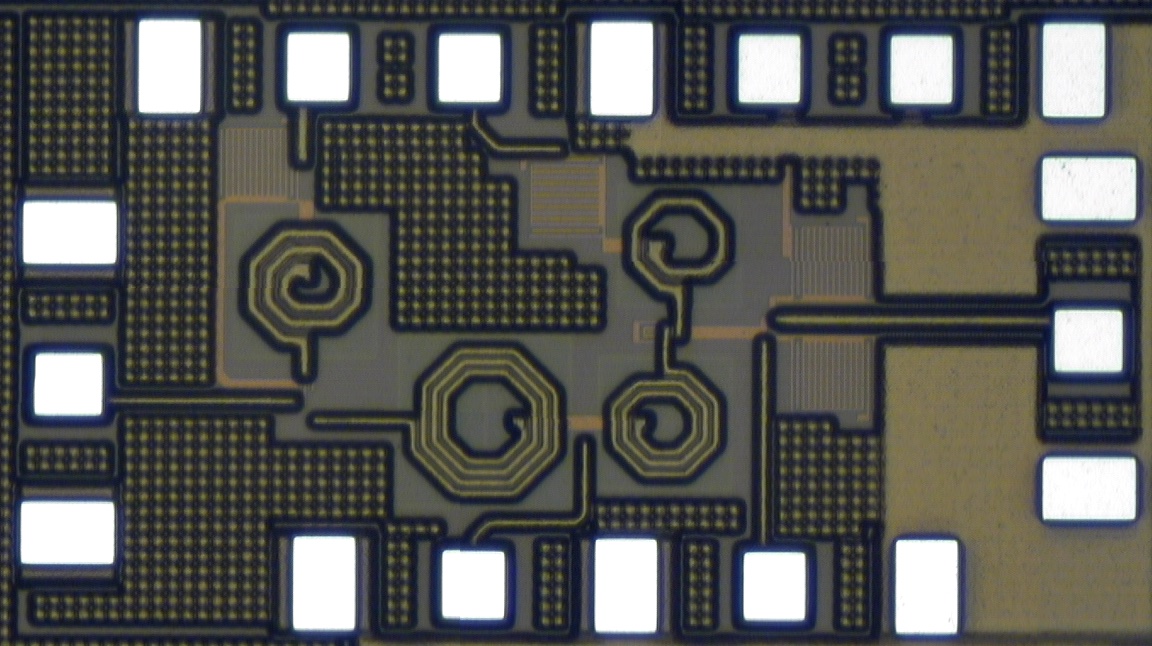

35-GHz Parametric Mixer

35-GHz Parametric Mixer

Upconversion using a nonlinear cap. No DC power required. Should work at much higher frequencies. 130-nm CMOS.

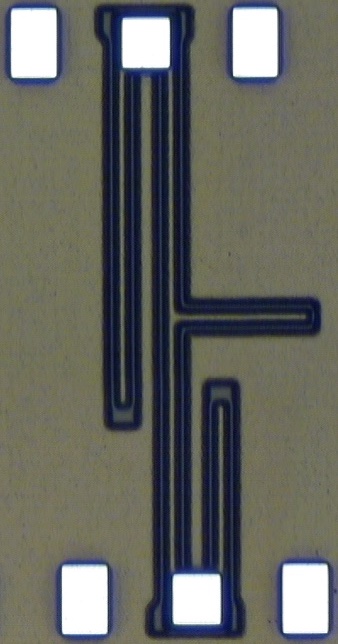

25-GHz Parametric Mixer

25-GHz Parametric Mixer

I don't think people tried these since WWII. The operating frequency was probably too low for lumped components in this case. 130-nm CMOS.

100-GHz Parametric Doubler

100-GHz Parametric Doubler

Humble doubler utilizing a nonlinear capacitance. I was surprised these things didn't appear sooner, but GaAs-based multipliers have achieved great performance. This approach gives some hope for tighter integration with other system components. 130-nm CMOS.

4-GHz Active Scatterer

4-GHz Active Scatterer

Wireless signals that bounce off this thing get phase modulated. It makes otherwise stationary communicators look like they are moving. This prevents wireless communicators from sitting in deep fades for too long and thus enables correction codes to do their job. Measurement results implied 4X improvement in WLAN coverage area. 130-nm CMOS.