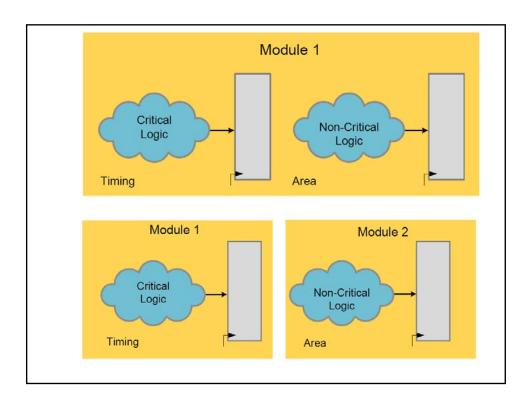

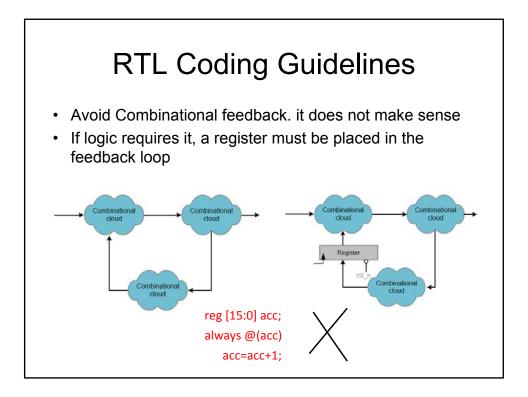

# Synthesis Guidelines

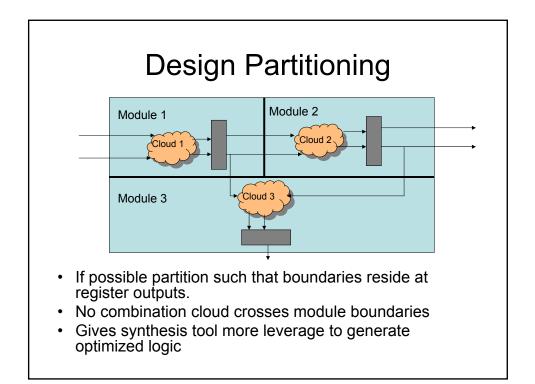

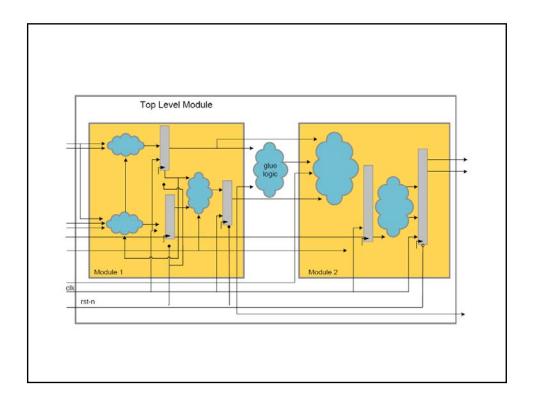

- Avoid glue logic that connects 2 modules

- Individual modules may satisfy timing conditions, but top level module may not.

- Such a logic should be made as a part of the combinational logic in one or the two modules.

- This may arise in debugging or after changing/correcting one of the interfaces of a module.

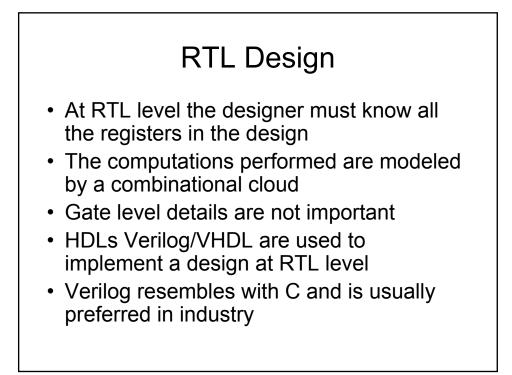

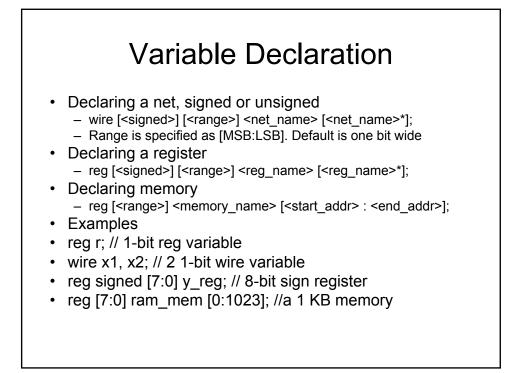

## Data Types

- Nets

- Nets are physical connections between components

- Nets always show the logic value of the driving components

- Many types of nets, we use wire in RTL

- Usually is the output of a combinational logic

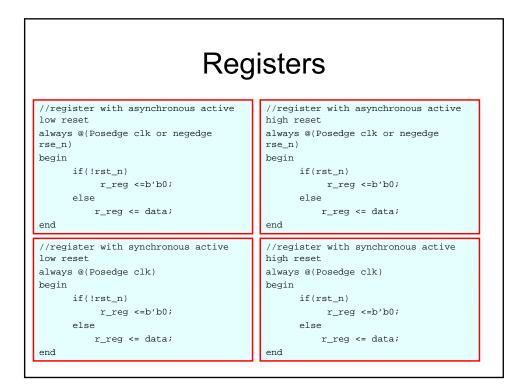

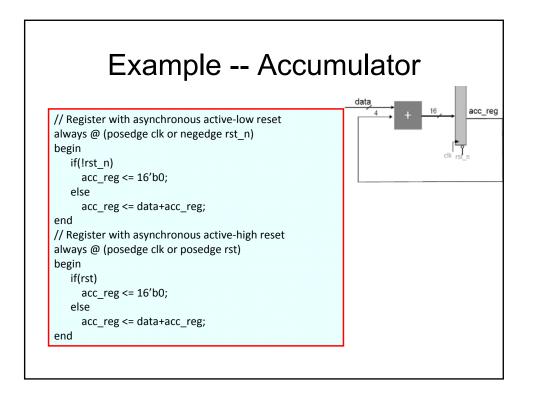

- Registers

- Implicit storage unless variable of this type is modified it retains previously assigned value

- Does not necessarily imply a hardware register

- Register type is denoted by reg

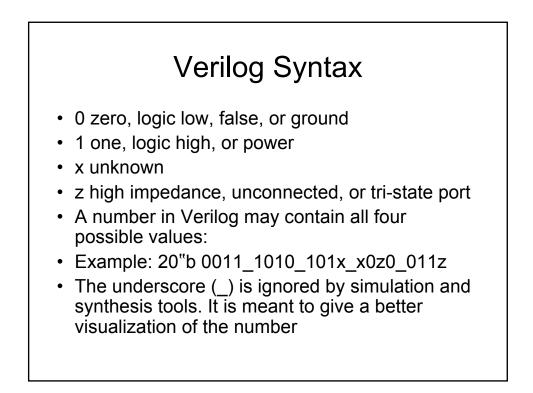

#### Constants

- Constants can be written in

- decimal (default)

- 13, 'd13

- binary

- 4'b1101

- octal

- 4'o15

- hexadecimal

- 4'hd

٠

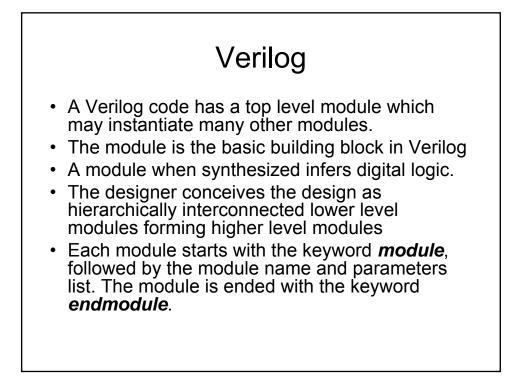

- To capture these details Verilog provides four levels of abstraction

- 1. Switch level

- 2. Gate level

- 3. Dataflow level

- 4. Behavioral or algorithmic level

### Levels of Abstraction

- Switch Level: The lowest level of abstraction is the switch or transistor Level Modeling

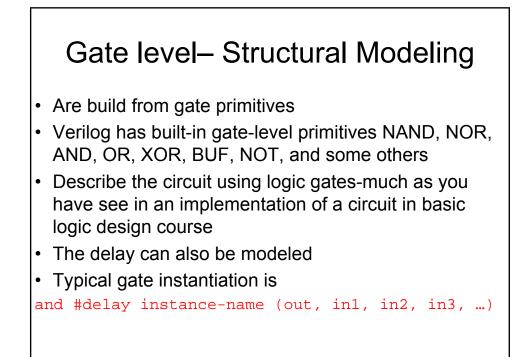

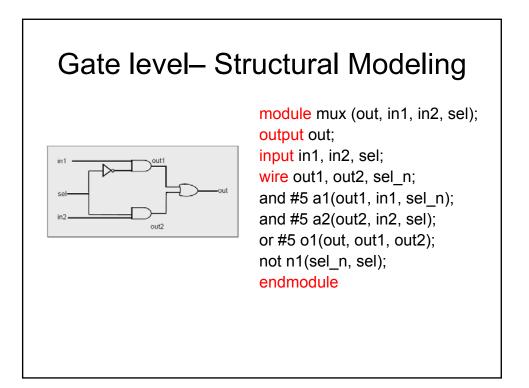

- **Gate Level**: Synthesis tools compile high level code and generate code at gate level

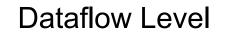

- **Dataflow Level**: The level of abstraction higher than the gate level

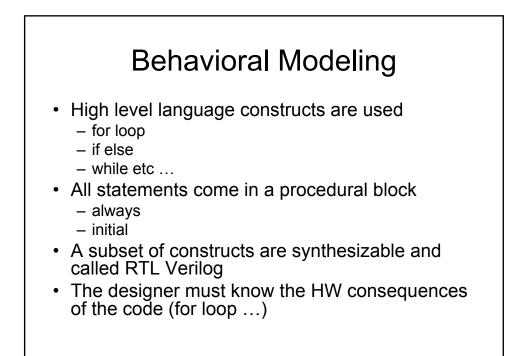

- **Behavioral Level**: In more complex digital designs, priority is given to the performance and behaviour at algorithmic level

|                 | Conditional Operator                                                                       |

|-----------------|--------------------------------------------------------------------------------------------|

| out =           | sel ? a : b;                                                                               |

| This state      | ment is equivalent to                                                                      |

| if(sel)<br>else | out = a;<br>out = b;                                                                       |

|                 | al operator can also be used to infer higher order multiplexers. The code infers a 4:1 mux |

| out = s         | el[1] ? ( sel[0] ? in3 : in2 ) : ( sel[0] ? in1 : in0 );                                   |

|                 |                                                                                            |

| <b>Relational Operators</b> |                 |                       |  |  |

|-----------------------------|-----------------|-----------------------|--|--|

| Relational Operator         | Operator Symbol | Operation performed   |  |  |

|                             | >               | Greater than          |  |  |

|                             |                 | Less than             |  |  |

|                             | >=              | Greater than or equal |  |  |

|                             | <=              | Less than or equal    |  |  |

| Bitwise Arithmetic Operators |                 |                     |  |  |

|------------------------------|-----------------|---------------------|--|--|

| Operator Type                | Operator Symbol | Operation performed |  |  |

| Bitwise                      | ~               | Bitwise negation    |  |  |

|                              | &               | Bitwise AND         |  |  |

|                              | ~&              | Bitwise NAND        |  |  |

|                              | l.              | Bitwise OR          |  |  |

|                              | ~               | Bitwise NOR         |  |  |

|                              |                 | Bitwise XOR         |  |  |

|                              | ^~ or ~^        | Bitwise XNOR        |  |  |

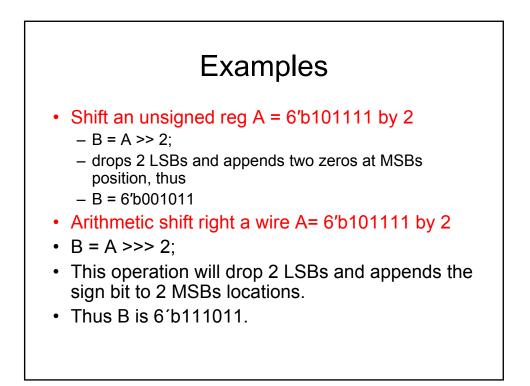

## Examples

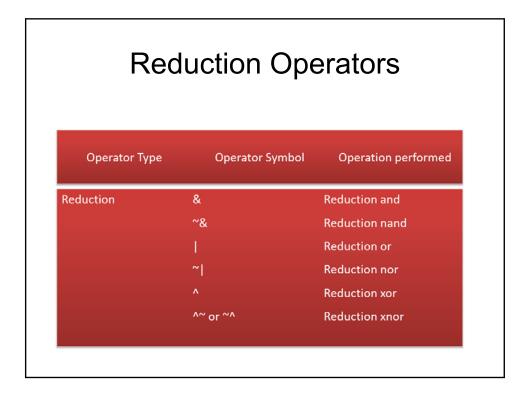

- Apply & reduction operator on a 4-bit number A=4'b1011

- assign out = &A;

- This operation is equivalent to performing a bitwise & operation on all the bits of A i.e.

- out = A[0] & A[1] & A[2] & A[3];

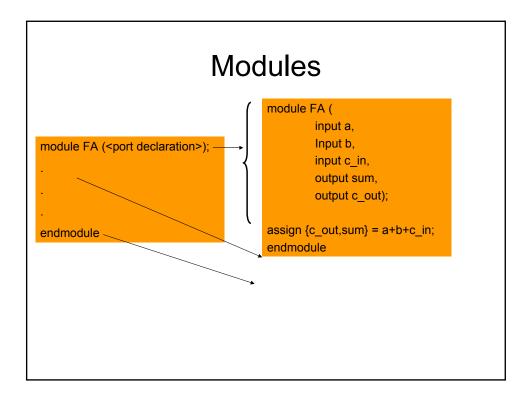

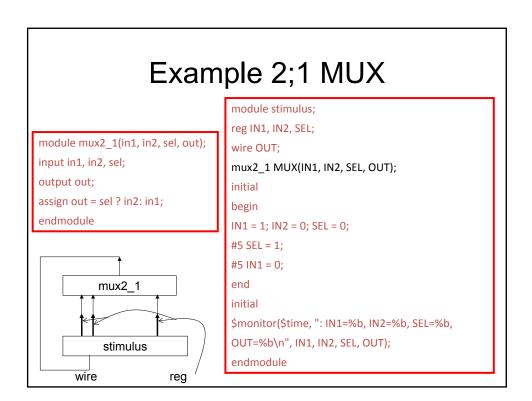

- At this level every expression is modeled with the assign keyword

- assign c=a+b

- The value on the wire c is continuously driven by the result of the arithmetic operation

- RHS must be a wire

- Operands my be wire or reg

## Example Dataflow Modeling

module adder\_4 (a, b, ci, s, co);

input [3:0] a, b;

input ci; output [3:0] s;

output co;

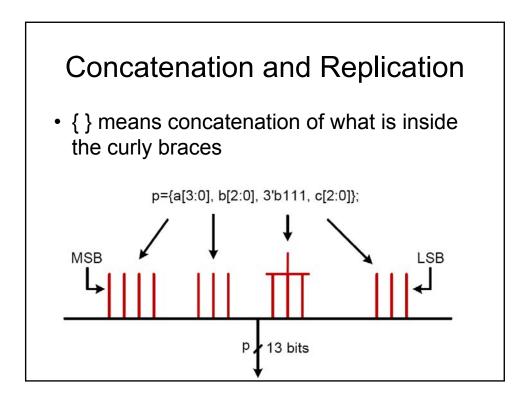

assign {co, s} = a + b + ci;

endmodule

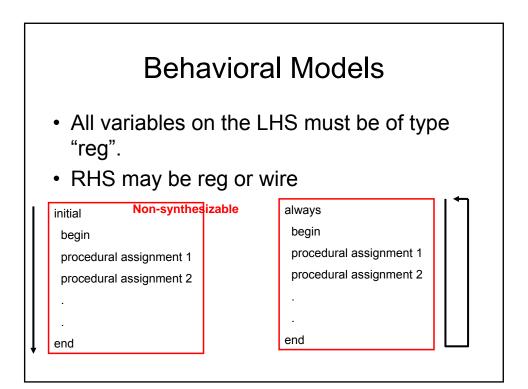

#### **Initial Block**

- · This block starts with initial keyword

- This is non synthesizable

- Non RTL

- · This block is used only in stimulus

- All initial blocks execute concurrently in an arbitrary order

- They execute until they come to a #delay operator

- Then they suspend, putting themselves in the event list delay time units in the future

- · At delay units, they resume executing where they left off

| reg sum, carry;<br>always @ (x or y)<br>begin<br>sum = x^y;<br>carry = x&y<br>end | <pre>reg sum, carry;<br/>always @ (x, y)<br/>begin<br/>sum = x^y;<br/>carry = x&amp;y<br/>End</pre> | reg sum, carry;<br>always @ (*)<br>begin<br>sum = x^y;<br>carry = x&y<br>end |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| (a)                                                                               | (b)                                                                                                 | (c)                                                                          |

|                                                                                   | rilog-2001 support of comi<br>-2001 style that only writes                                          |                                                                              |

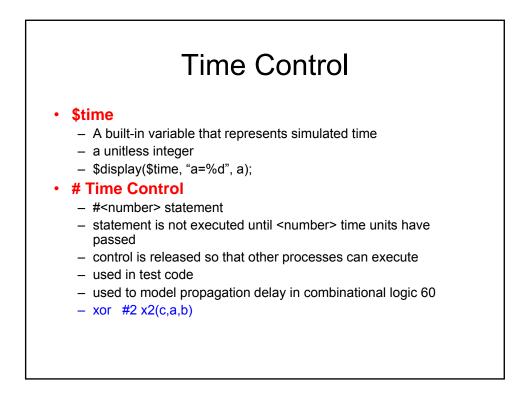

## @ Time Control

- @(\*)

- @(expression)

- @(expression or expression or ...)

- @(posedge onebit)

- @(negedge onebit)

- · do not execute statement until event occurs

- @(clk) is same as @(posedge clk or negedge clk)

#### **Generating Clock in Stimulus**

**initial** // All the initializations should be in the initial block **begin**

clk = 0; // clock signal must be initialized to 0

# 5 rst\_n = 0; // pull active low reset signal to low

# 2 rst\_n=1; // pull the signal back to high

end

always // generate clock in an always block

#10 clk=(~clk);

#### **Case Statement** MUX whose output depends module mux4\_1(in1, in2, in3, in4, sel, out); on sel input [1:0] sel; input [15:0] in1, in2, in3, in3; output [15:0] out; If multiple matches, the first reg [15:0] out; one is executed only always @(\*) case (sel) 2'b00: out = in1; @(\*) automatically poulates 2'b01: out = in2; the sensitivity list with all 2'b10: out = in3; varaibles in the RHS 2'b11: out = in4; default: out = 16'bx; endcase Case is inside an always endmodule block

| Casex and Casez                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>To make comparison with the "don"t care"</li> <li>– casez takes z as don"t care</li> <li>– casex takes z and x as don"t care</li> </ul>         |

| always @(op_code)<br>begin<br>casez (op_code)<br>4'b1???: alu_inst(op_code);<br>4'b01??: mem_rd(op_code);<br>4'b001?: mem_wr(op_code);<br>endcase<br>end |