### Chapter 6

Registers and Counters

FALL 2011 CSE3201

# Chapter 6

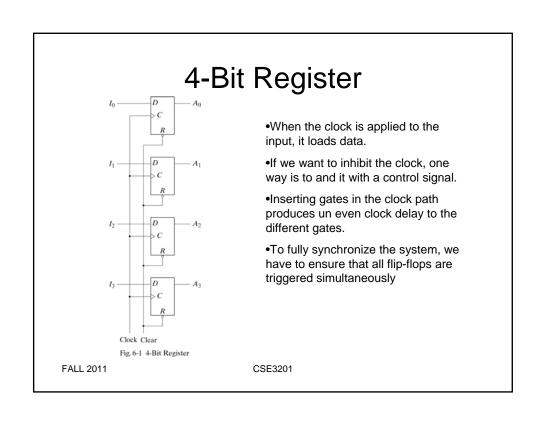

- A register is a group of flip-flops each id capable of storing one bit of information.

- A counter is a register that go through a predetermined sequence of states.

FALL 2011 CSE3201

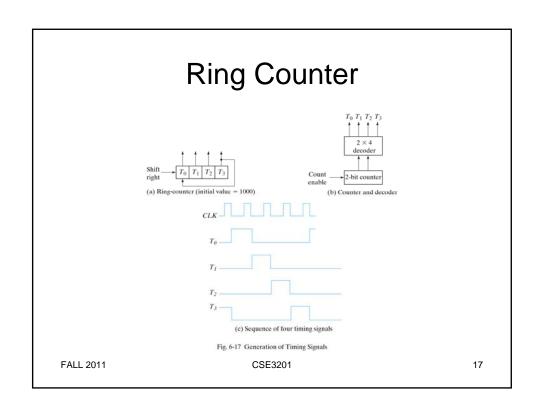

### Counters

- Ripple counters: the flip-flop output transition serves as a source for triggering other flip-flops (C input is triggered by flipflop output rather than a common clock).

- Asynchronous counters: The CLK input of all flip-flops receive common clock.

Transitions are triggered by combinatorial logic of other flip-flop outputs

FALL 2011 CSE3201

# Binary Ripple Counters Count FALL 2011 Binary Ripple Counters Count Fip Ao Count F

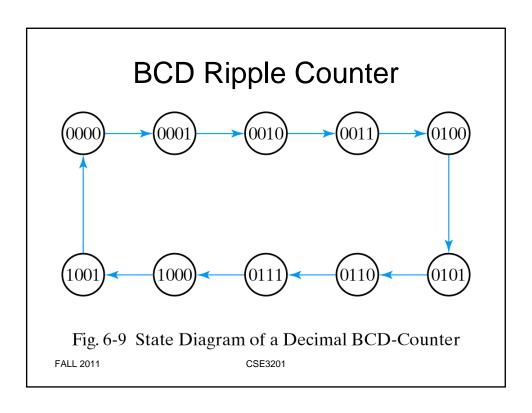

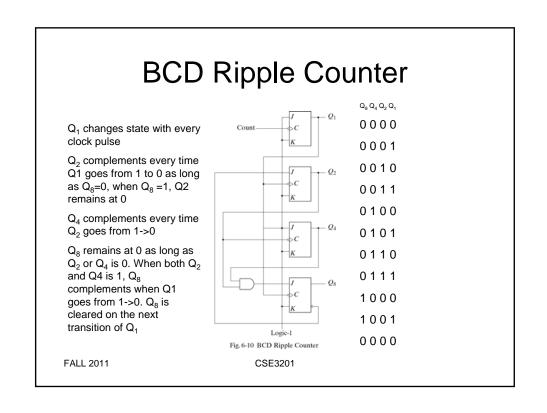

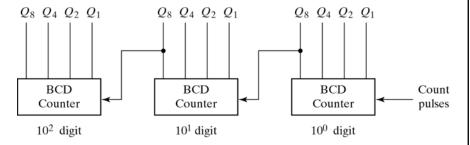

# Three Decades Decimal BCD Counter

Fig. 6-11 Block Diagram of a Three-Decade Decimal BCD Counter

The input to the second and third stage comes from  $Q_8$  to the previous stage. When  $Q_8$  goes from 1 o zero, that is if  $Q_8$  goes to 0, it triggers the count in the higher stage while its own count goes to zero

FALL 2011 CSE3201

### Synchronous Counters

- •Clock pulses are applied to all flip-flops

- •The least significant bit is complemented every clock cycle.

- •The flip-flop in any position is complemented when all the bits in the lower significant positions are equal to 1.

- •The flip-flops trigger on the positive, the polarity of the clock is not essential here as it was in the ripple counter case.

Fig. 6-12 4-Bit Synchronous Binary Counter

FALL 2011 CSE3201

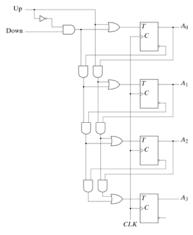

# **Up-Down Binary Counter**

- •The bit in the least significant bit is complemented every clock cycle.

- •For count down, a bit in any position is complemented if all the bits in the lower positions are 0's

- •BCD counters could be implemented using the techniques we learnt in the previous chapter

Fig. 6-13 4-Bit Up-Down Binary Counter

FALL 2011

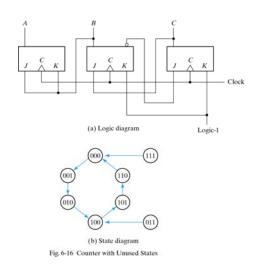

### Counters with unused states

CSE3201

Analyze the circuit to know what will be the effect of the system being in one of the unused states due to error.

If the system goes eventually to the correct counting sequence, it is a self correcting counter

FALL 2011

CSE3201

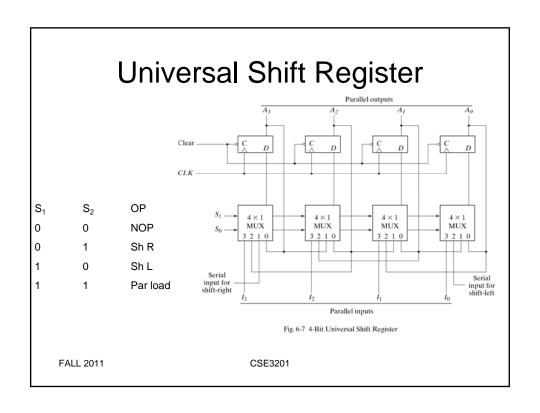

### Example

```

//HDL Example 6-1

//Behavioral description of

//Universal shift register

// Fig. 6-7 and Table 6-3

module shftreg (s1,s0,Pin,Ifin,rtin,A,CLK,CIr);

input s1,s0;

//Select inputs

input Ifin, rtin;

input CLK,Clr;

//Serial inputs

//Clock and Clear

input [3:0] Pin;

//Parallel input

output [3:0] A;

//Register output

reg [3:0] A;

always @ (posedge CLK or negedge CIr)

if (\simClr) A = 4'b0000;

else

case ({s1,s0})

2'b00: A = A;

//No change

2'b01: A = {rtin,A[3:1]}; //Shift right

2'b10: A = {A[2:0], lfin}; //Shift left

2'b11: A = Pin;

//Parallel load input

endcase

endmodule

FALL 2011

CSE3201

```

### Example

```

//HDL Example 6-2

//One stage of shift register

module stage(i0,i1,i2,i3,Q,select,CLK,Clr);

//Structural description of

input i0,i1,i2,i3,CLK,Clr;

//Universal shift register(see Fig.6-7)

input [1:0] select;

module SHFTREG (I,select,Ifin,rtin,A,CLK,CIr);

output Q;

reg Q;

//Parallel input

input [3:0] I;

reg D;

input [1:0] select;

//Mode select

//4x1 multiplexer

input lfin,rtin,CLK,Clr; //Serial inputs,clock,clear

always @ (i0 or i1 or i2 or i3 or select)

case (select)

output [3:0] A;

//Parallel output

2'b00: D = i0;

//Instantiate the four stages

2'b01: D = i1;

stage ST0 (A[0],A[1],Ifin,I[0],A[0],select,CLK,Clr);

2'b10: D = i2;

2'b11: D = i3;

stage ST1

(A[1],A[2],A[0],I[1],A[1],select,CLK,Clr);

endcase

//D flip-flop

stage ST2

(A[2],A[3],A[1],I[2],A[2],select,CLK,Clr);

always @ (posedge CLK or negedge Clr)

stage ST3 (A[3],rtin,A[2],I[3],A[3],select,CLK,Clr);

if (\simClr) Q = 1'b0;

else Q = D;

endmodule

endmodule

FALL 2011

CSE3201

```

# Example

```

//HDL Example 6-3

//Binary counter with parallel load

//See Figure 6-14 and Table 6-6

module counter (Count,Load,IN,CLK,Clr,A,CO);

input Count,Load,CLK,Clr;

//Data input

//Output carry

input [3:0] IN;

output CO;

output [3:0] A;

//Data output

reg [3:0] A;

assign CO = Count & ~Load & (A == 4'b1111);

always @ (posedge CLK or negedge Clr)

if (~Clr) A = 4'b0000;

else if (Load) A = IN;

else if (Count) A = A + 1'b1;

// no change, default condition

else A = A;

endmodule

```

FALL 2011 CSE3201