### Register Transfer Level

#### **ECE470**

#### **RTL**

- A digital system is represented at the register transfer level by these three components

- 1. The set of registers in the system

- 2. The operation that are performed on the data stored in the registers

- 3. The control that supervises the sequence of operations in the system.

- The operations executed on the information stored in the registers are elementary operations and performed in parallel during one clock cycle.

#### **RTL**

Comma is used to separate 2 or more operations that are executed in the same time

```

If (T3=1) then (R2 \leftarrow R1, R1 \leftarrow R2)

```

That is possible with registers that have edge triggered flip-flop

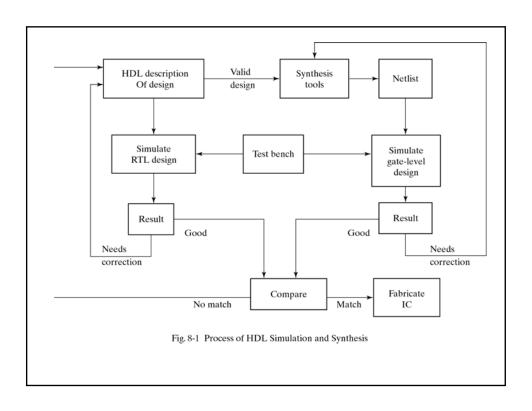

## **HDL Operations**

- Arithmetic: + \* / %

- Logic (bit wise): ~ & | ^

- Logical ! && ||

- Shift >> << {,}

- Relational > < == != >= <=

- In shifting, the vacant bits are filled with zeros

## **Loop Statements**

```

integer count initial begin

begin clock = 1'b0;

count = 0; end

while (count <0) repeat (16)

#5 count = count+1; #5 clock = ~ clock;

```

end end

```

Loop Statements

module decoder

input [1:0] IN;

assign Y=s ? L1: L0;

output [3:0]Y;

Or

reg [3:0]Y;

always @(L1 or L0 or S)

integer I;

if (S) Y=I1;

always @(IN)

else Y=I0;

for (I=0; I<=3; I=I+1)

if (IN == I) Y[I]=1;

else Y[I}=0;

endmodule

```

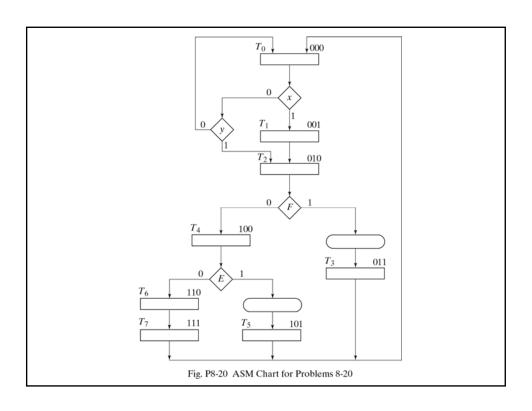

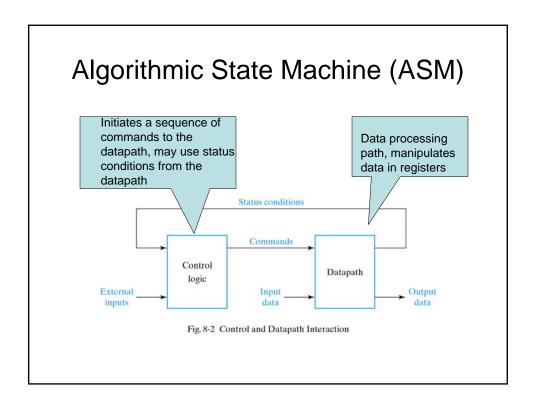

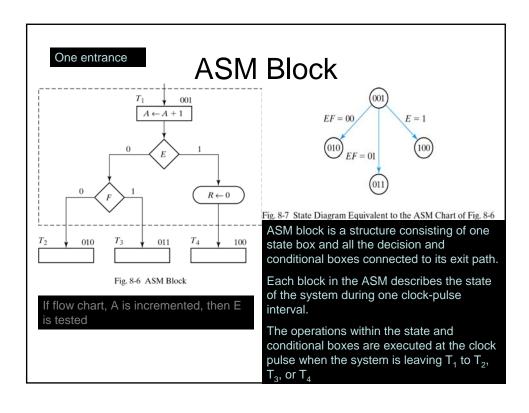

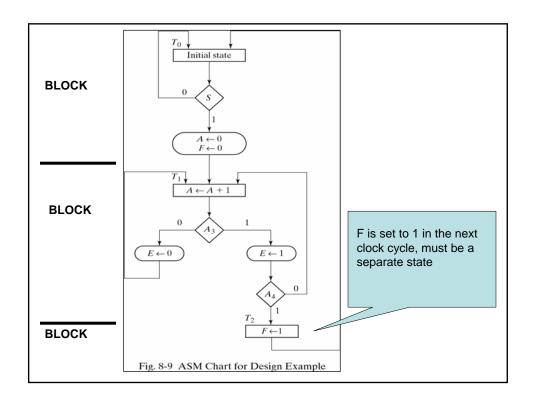

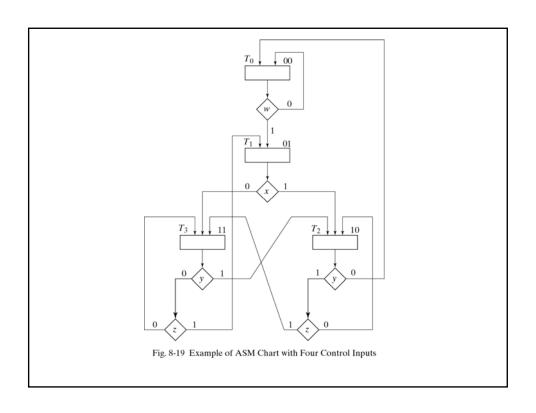

#### **ASM**

- ASM is similar to flowchart in the sense that it specifies a sequence of procedural steps and decision paths for an algorithm.

- However, ASM is interpreted differently than a flowchart. While the flow chart is interpreted as a sequence of operations, ASM describes the sequence of events as well as the timing relationship between the states (as we will see shortly).

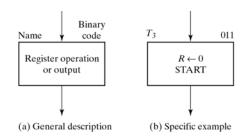

#### State Box

Fig. 8-3 State Box

The state is given a symbolic name (T3)

Binary code for the assigned state (011)

The operations that are performed in this state  $R \leftarrow 0$ ; and START could be an output signal is generated to start some operation

The operation is performed when we leave  $T_3$  to the next state

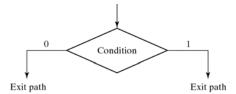

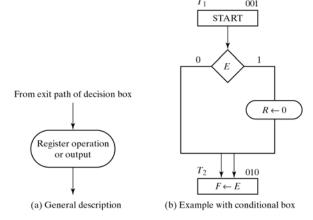

#### **Decision Box**

Fig. 8-4 Decision Box

#### **Conditional Box**

Fig. 8-5 Conditional Box

Input to the conditional box must come from one of the exit paths of a decision box.

The register operation or outputs listed inside the conditional box are generated during a given state, if the input condition is satisfied of course

#### **ASM**

- The operation in the state box or conditional box are nott executed in the current state.

- Rather, a control signal is asserted in the current state if Q0 is 1 and the operation is done at the transition from this state to the next one (with the next clock cycle)

### Design Example

- Design a system with 2 flip-flops E and F, and one 4 bit binary counter (A<sub>4</sub>, A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub>).

- A start signal initiates the operation by clearing A and F.

- Then the counter is incremented by one starting from the next clock pulse and continues to increment until the operation stops. A<sub>3</sub> and A<sub>4</sub> determine the operations.

- If  $A_3 = 0$ , E is cleared and continue

- If A3=1, E is set; then if A4=0 continue, if A4=1 F is set to 1 on the next clock cycle and the system stops.

| Co      | oun   | ter |                | Flip- | Flops |                                     |                |  |

|---------|-------|-----|----------------|-------|-------|-------------------------------------|----------------|--|

| $A_{A}$ | $A_3$ | Α,  | A <sub>1</sub> | Ε     | F     | Condition                           | State          |  |

| 0       | 0     | 0   |                | 1     | 0     | $A_3=0, A_4=0$                      | $T_1$          |  |

| 0       |       | 0   |                | 0     | 0     |                                     |                |  |

| 0       | 0     | 1   | 0              | 0     | 0     |                                     |                |  |

| 0       | 0     | 1   | 1              | 0     | 0     |                                     |                |  |

| 0       | 1     | 0   | 0              | 0     | 0     | Λ –1 Λ –0                           |                |  |

|         | 1     | 0   |                | 1     | 0     | $A_3 = 1, A_4 = 0$                  |                |  |

|         |       | 1   |                | 1     | 0     |                                     |                |  |

| _       |       |     | -              | -     | -     |                                     |                |  |

| 0       | 1     | 1   | 1              | 1     | 0     |                                     |                |  |

| 1       | 0     | 0   | 0              | 1     | 0     | $A_3 = 0, A_4 = 1$                  |                |  |

| 1       | 0     | 0   | 1              | 0     | 0     | 3 . 4                               |                |  |

| 1       | 0     | 1   | 0              | 0     | 0     |                                     |                |  |

| 1       | 0     | 1   | 1              | 0     | 0     |                                     |                |  |

| 1       | 1     | 0   | 0              | 0     | 0     | A <sub>3</sub> =1,A <sub>4</sub> =1 |                |  |

| 1       | 1     | 0   | 1              | 1     | 0     |                                     | T <sub>2</sub> |  |

| 1       | 1     | 0   | 1              | 1     | 1     |                                     | T <sub>o</sub> |  |

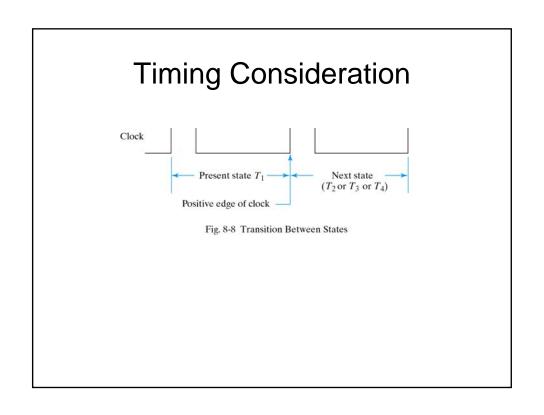

## Timing Sequence

- That illustrates the difference between ASM and flowchart.

- When the system is in state 1011, It checks A<sub>3</sub> is 0, so it sets E to 0 and increment counter to 1100, the next cycle will start with 1100 and E set to 0.

- Then checks A<sub>3</sub> and A<sub>4</sub> (both are 1), it sets E to 1, and increments counter.

- Next cycle counter is 1101, and E=1 and now it is in state 2

- Then it set F to 1 and goes to state 0

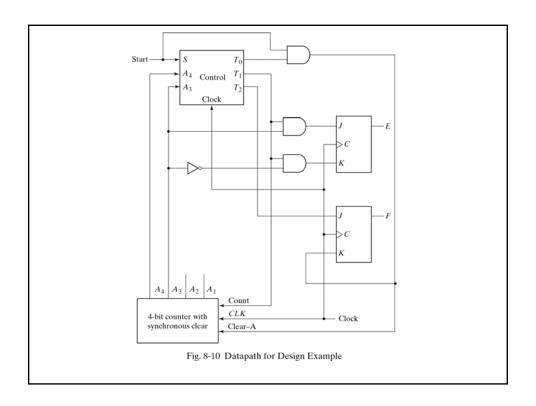

#### Datapath Design

- The requirements for the design of the datapath are specified in the state and conditional boxes.

- The control logic is determined from the decision and the required state transition.

- A look at the datapath design of the previous example.

#### Datapath design

- In state T<sub>0</sub>, clear the counter and the F flipflop (the and gate and f inputs).

- In state T₁, if A₃=0, set E←0 (will generate 01 on the JK inputs of E if the state is T1).

- In state T<sub>1</sub>, if A<sub>3</sub>A<sub>4</sub>=10; E ←0 (note the inputs of E).

- In state T<sub>2</sub>, if A<sub>3</sub>A<sub>4</sub>=11, F ← 1, and (the F-F is set).

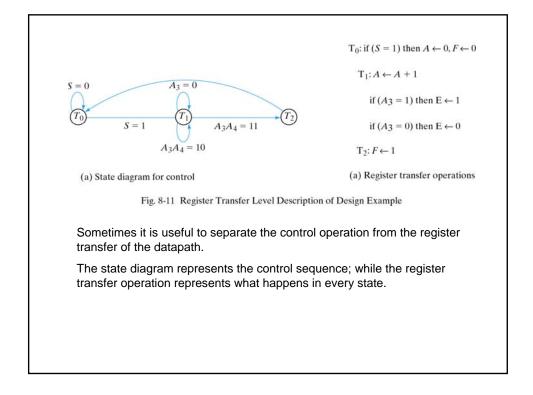

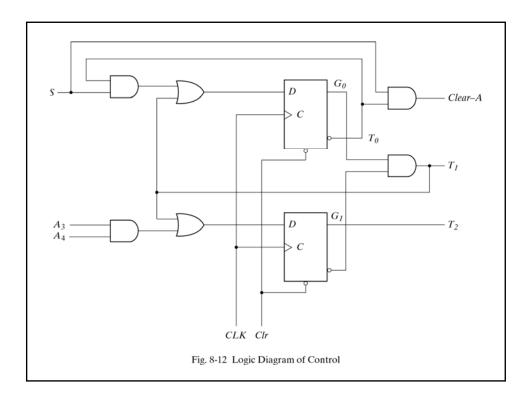

#### State Table

- The state diagram can be converted into a state table.

- Three states (T<sub>0</sub>, T<sub>1</sub>, and T<sub>2</sub>), represents as the output of two registers (G<sub>1</sub> G<sub>0</sub>) as 00, 01, and 11.

- The following table shows the state table for the previous example.

|                                          | Present State |    | Inputs next State |    |                | tate                                             | Outputs                                        |    |    |    |

|------------------------------------------|---------------|----|-------------------|----|----------------|--------------------------------------------------|------------------------------------------------|----|----|----|

| Present (symbol)                         | G1            | G0 | s                 | А3 | <b>A4</b>      | G1                                               | G0                                             | T0 | T1 | T2 |

| TO .                                     | 0             | 0  | . 0               | Х  | Х              | . 0                                              | 0                                              | .1 | 0  | 0  |

| T0                                       | 0             | 0  | 1                 | Χ  | Χ              | 0                                                | 1                                              | 1  | 0  | 0  |

|                                          |               |    |                   |    |                |                                                  |                                                |    |    |    |

| T1                                       | 0             | 1  | Х                 | 0  | Χ              | 0                                                | 1                                              | 0  | 1  | 0  |

| T1                                       | 0             | 1  | Х                 | 1  | 0              | 0                                                | 1                                              | 0  | 1  | 0  |

| T1                                       | 0             | 1  | Х                 | 1  | 1              | 1                                                | 1                                              | 0  | 1  | 0  |

| Т2                                       | 1             | 1  | х                 | Х  | X              | 0                                                | 0                                              | 0  | 0  | 1  |

| $T_0 = G_0'$ $T_1 = G_1'G_0$ $T_2 = G_1$ |               |    | ı                 |    | D <sub>G</sub> | =T <sub>1</sub> A <sub>3</sub> =T <sub>0</sub> S | <sub>3</sub> A <sub>4</sub><br>+T <sub>1</sub> |    |    |    |

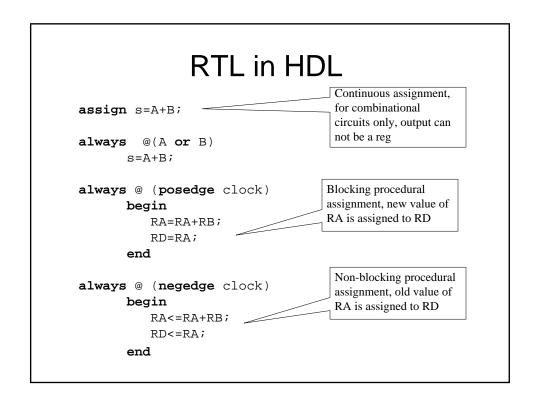

## **HDL** Description

- The description could be one three different levels

- Behavioral description on the RTL level

- Behavior description on the algorithmic level

- Structural description

- Note that the algorithmic level, is used only to verify the design *ideas* in the early stages. Some of the constructs might not be *synthesizable*

- Following RTL behavior description

```

always @ (S or A or pstate)

case (pstate)

//RTL description of design example module Example_RTL (S,CLK,Clr,E,F,A);

T0: if(S) nstate = T1;

T1: if(A[3] & A[4]) nstate = T2;

//Specify inputs and outputs

//See block diagram Fig. 8-10

T2: nstate = T0:

input S,CLK,Clr;

default: nstate = T0;

endcase

output E,F;

//Register transfer operatons

output [4:1] A;

//See list of operations Fig.8-11(b)

//Specify system registers

reg [4:1] A;

//A register

always @(posedge CLK)

case (pstate)

reg E, F;

//E and F flip-flops

reg [1:0] pstate, nstate; //control register

T0: if(S)

begin

parameter T0 = 2'b00, T1 = 2'b01, T2 = 2'b11;

//Encode the states

A \le 4'b0000;

F \le 1'b0;

//State transition for control logic

end

//See state diagram Fig. 8-11(a)

T1:

always @(posedge CLK or negedge Clr)

begin

if (~Clr) pstate = T0; //Initial state

A \le A + 1'b1;

else pstate <= nstate; //Clocked

if (A[3]) E <= 1'b1;

operations

else E <= 1'b0;

end

T2: F <= 1'b1;

endcase

endmodule

```

#### **Testing**

- Note that because we used non-blocking assignment we did not have to worry about the order of the statements in every state.

- Had we used a blocking assignment, we have to worry about the order.

## **Testing**

```

Example_RTL dsexp (S,CLK,Clr,E,F,A);

//HDL Example 8-3

initial

//Test bench for design example

begin

module test_design_example;

CIr = 0;

reg S, CLK, Clr;

S = 0;

wire [4:1] A;

CLK = 0;

wire E, F;

#5 Clr = 1; S = 1;

//Instantiate design example

repeat (32)

endmodule

begin

#5 CLK = ~ CLK;

end

end

initial

monitor("A = \%b E = \%b F = \%b time = \%0d", A,E,F,$time);

```

## Structural Description

## Structural Description

- //HDL Example 8-4

- //-----

- //Structural description of design example

- //See block diagram Fig. 8-10

- module Example\_Structure (S,CLK,Clr,E,F,A);

- input S,CLK,Clr;

- output E,F;

- output [4:1] A;

- //Instantiate control circuit

- control ctl

- (S,A[3],A[4],CLK,Clr,T2,T1,Clear);

- //Instantiate E and F flip-flips

- E\_F EF (T1,T2,Clear,CLK,A[3],E,F);

- //Instantiate counter

- counter ctr (T1,Clear,CLK,A);

- endmodule

- //Control circuit (Fig. 8-12)

- module control

- (Start, A3, A4, CLK, Clr, T2, T1, Clear);

- input Start,A3,A4,CLK,Clr;

- output T2,T1,Clear;

- wire G1,G0,DG1,DG0;

- //Combinational circuit

- assign DG1 = A3 & A4 & T1,

- DG0 = (Start & ~G0) | T1,

- T2 = G1

- $T1 = G0 \& \sim G1$

- Clear = Start & ~G0;

- //Instantiate D flip-flop

- DFF G1F (G1,DG1,CLK,Clr),

- G0F (G0,DG0,CLK,Clr);

- endmodule

#### Structural Description

- //D flip-flop

- module DFF (Q,D,CLK,Clr);

- input D,CLK,Clr;

- output Q;

- reg Q;

- always @ (posedge CLK or negedge Clr)

- if (~Clr) Q = 1'b0;

- else Q = D;

- endmodule

- //E and F flipf-lops

- module E\_F

- (T1,T2,Clear,CLK,A3,E,F);

- input T1,T2,Clear,CLK,A3;

- output E,F;

- wire E,F,JE,KE,JF,KF;

- //Combinational circuit

- assign JE = T1 & A3,

- $KE = T1 \& \sim A3$ ,

- JF = T2,

- KF = Clear;

- //Instantiate JK flipflop

- JKFF EF (E,JE,KE,CLK),

- FF (F,JF,KF,CLK);

- endmodule

### Structural Description

- //JK flip-flop

- module JKFF (Q,J,K,CLK);

- input J,K,CLK;

- output Q;

- reg Q;

- always @ (posedge CLK)

- case ({J,K})

- 2'b00: Q = Q;

- 2'b01: Q = 1'b0;

- 2'b10: Q = 1'b1;

- 2'b11: Q = ~Q;

- endcase

- endmodule

- //counter with synchronous clear

- module counter (Count,Clear,CLK,A);

- input Count,Clear,CLK;

- output [4:1] A;

- reg [4:1] A;

- always @ (posedge CLK)

- if (Clear) A<= 4'b0000;

- else if (Count) A <= A + 1'b1;

- else A <= A;</li>

- · endmodule

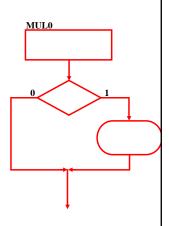

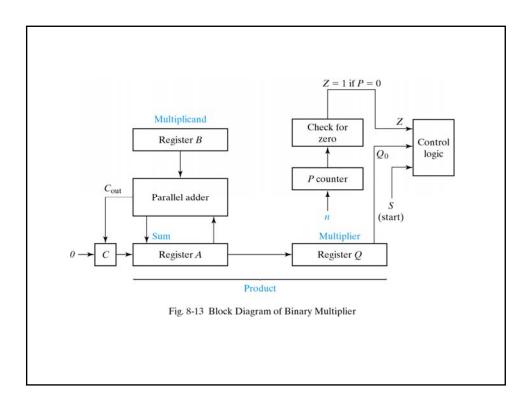

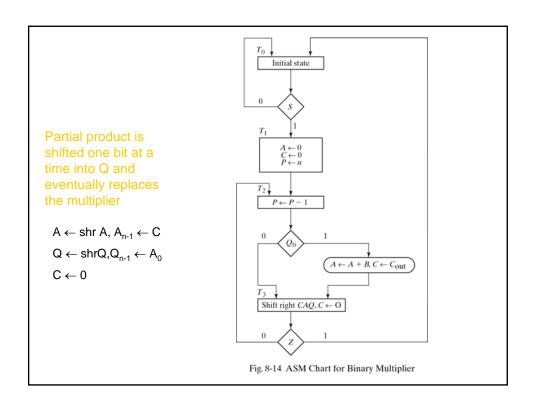

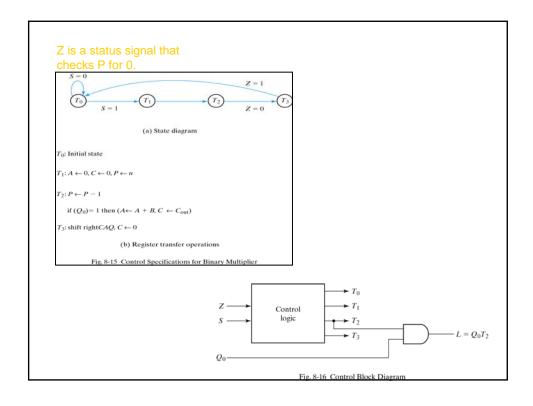

## **Binary Multiplier**

- We did this before using combinational circuit (adders, gaters, ..).

- Use one adder and shift registers.

- Instead of shifting multiplicand to the left, shift the partial product to the right.

| 23  | 10111     |

|-----|-----------|

| 19  | 10011     |

|     | 10111     |

|     | 10111     |

|     | 00000     |

|     | 00000     |

|     | 10111     |

| 437 | 110110101 |

## **Binary Multiplier**

- Assume that the multiplicand in B, and the multiplier in Q.

- P contains *n* the length of the multiplier

| $\bigcirc$ . |     |   |

|--------------|-----|---|

| Stata        | しつわ |   |

| State        | Tab | ı |

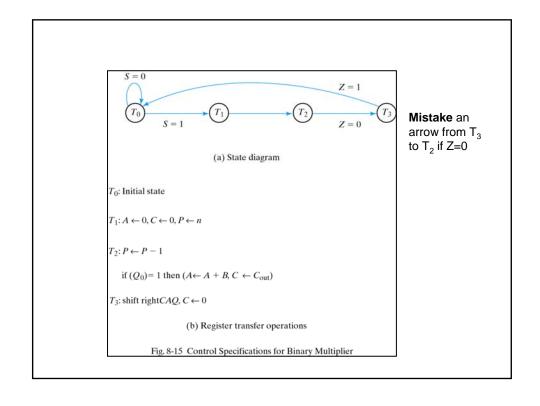

| Present State |    | Inp | uts | next S | State | Out | Outputs |    |    |  |

|---------------|----|-----|-----|--------|-------|-----|---------|----|----|--|

| G1            | G0 | S   | Z   | G1     | G0    | T0  | T1      | T2 | Т3 |  |

|               |    |     |     |        |       |     |         |    |    |  |

| 0             | 0  | 0   | Χ   | 0      | 0     | 1   | 0       | 0  | 0  |  |

| 0             | 0  | 1   | Χ   | 0      | 1     | 1   | 0       | 0  | 0  |  |

| 0             | 1  | Χ   | Χ   | 1      | 0     | 0   | 1       | 0  | 0  |  |

| 1             | 0  | Χ   | Χ   | 1      | 1     | 0   | 0       | 1  | 0  |  |

| 1             | 1  | Χ   | 0   | 1      | 0     | 0   | 0       | 0  | 1  |  |

| 1             | 1  | Χ   | 1   | 0      | 0     | 0   | 0       | 0  | 1  |  |

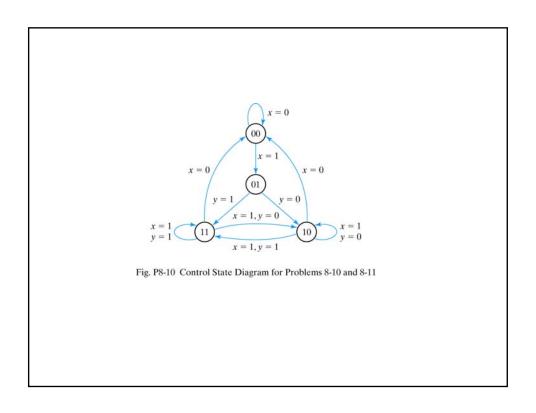

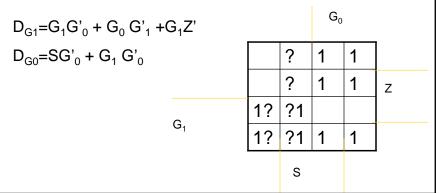

# Controller Design

We can use conventional sequential circuit design for the controller, if we did using 2 D type Flip-Flops

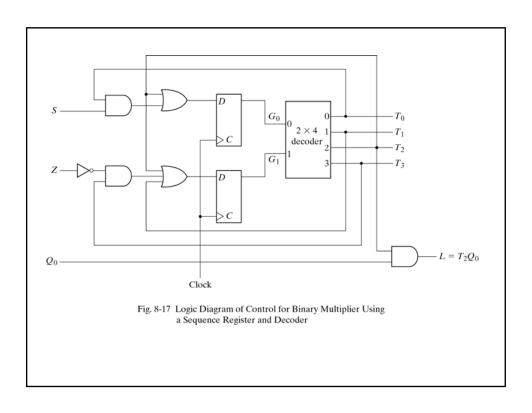

#### Sequence Register and Decoder

- If the number of variables is large, conventional design is difficult.

- Need specialized methods for the control design.

- Uses a register to control the states, and a decoder to provide an output corresponding to each of the states.

- A register with n flip-flops can have up to 2<sup>n</sup> states, and n-to-2<sup>n</sup> line decoder has up to 2<sup>n</sup> outputs.

#### Sequence Register and Decoder

- The circuit could be obtained directly from the table by inspection (keep in mind that the states are available as inputs).

- Directly from the table, there are three 1's for G<sub>1</sub>, which means

$$D_{G1} = T_1 + T_2 + T_3 \overline{Z}$$

$$D_{G0} = T_0 S + T_2$$

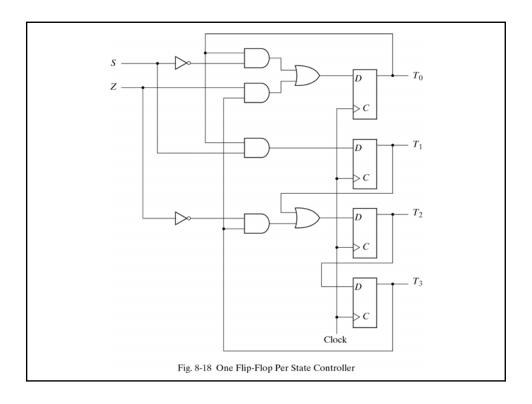

#### One Flip-Flop per State

- We need n flip-flops for every state

- In this case, we need 4 flip-flops.

- The circuits are very simple to implement and can be obtained directly from the state diagram.

- For example, we move from state 0 to 1 if S=1 which means D<sub>T1</sub>=T<sub>0</sub>S

### One Flip-Flop per State

$$D_{T0} = T_0 \overline{S} + T_3 Z$$

$$D_{T1} = T_0 S$$

$$D_{T2} = T_1 + T_3 \overline{Z}$$

$$D_{T3} = T_2$$

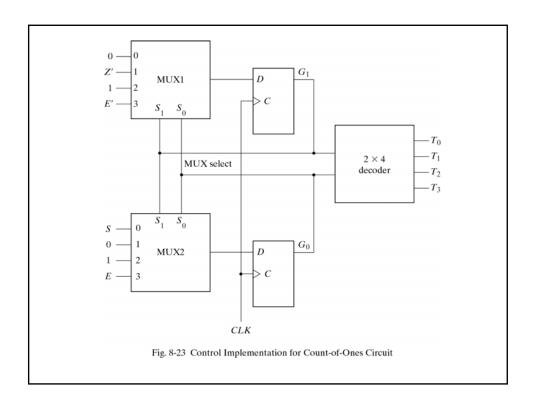

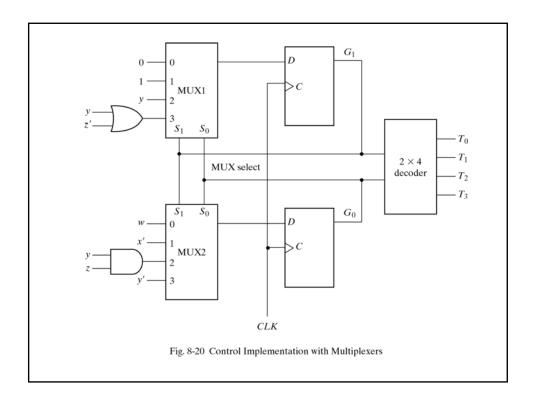

### Design with multiplexers

- The previous design consists of flip-flops, decoder, and gates.

- Replacing gates with multiplexers results in a regular pattern of the design.

- First level contains multiplexers (possibly added gates, but only one level.

- The second level is the registers to hold the present state information

- The last stage has a decoder that provides a separate output for every state

| Presen | t Stata | nov            | t State | I/P   | innuto         | n     |

|--------|---------|----------------|---------|-------|----------------|-------|

| G1     | G0      | G1             |         | cond. | inputs<br>MUX1 | MUX2  |

| 0      | 0       | <sub>/</sub> 0 | 0       | w'    |                |       |

| 0      | 0       | 0              | 1       | W     | 0              | W     |

| 0      | 1       | 1              | 0       | х     |                |       |

| 0      | 1       | 1              | 1       | x'    | 1              | χ'    |

| 1      | 0       | 0              | 0       | y'    |                |       |

| 1      | 0       | 1              | 0       | yz'   | yz'+yz=y       | yz    |

| 1      | 0       | 1              | 1       | yz    |                |       |

| 1      | 1       | 0              | 1       | y'z   |                |       |

| 1      | 1       | 1              | 0       | у     | y+y'z=y+z      | y'z+y |

| 1      | 1       | 1              | 1       | y'z'  |                |       |

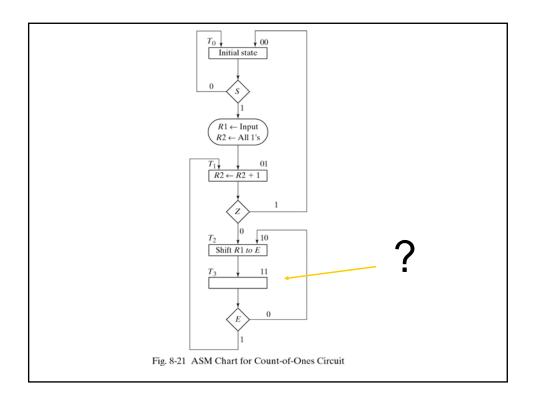

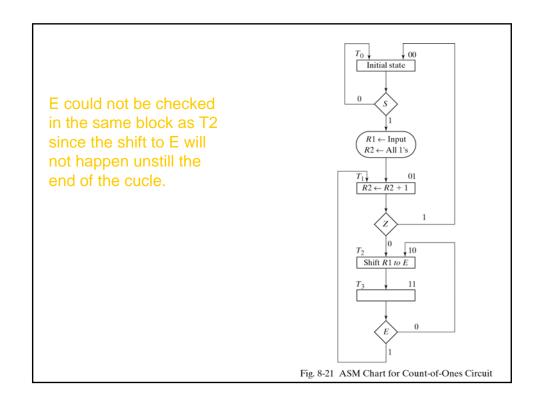

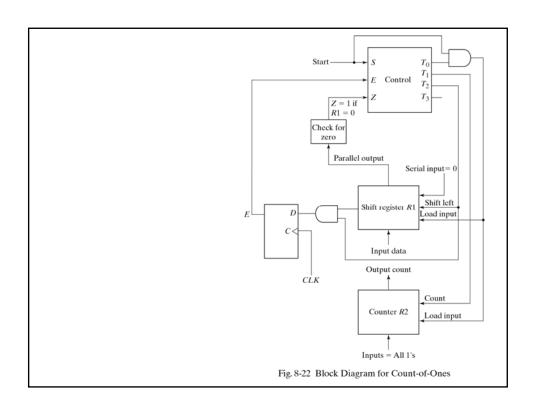

## Counting the number of 1's

- The system counts the number of 1's in R1, and set R2 accordingly.

- The bits in R1 are shifted one at a time, checking if the shifted out bit is 1 or 0, and incrementing R2

- Z is a signal to indicate if R1 contains all 0's or not.

- E is the output of the flip-flop (the shifted out bit).

|         | Cor | ntro  | l (co | unting     | of 1's     | s)   |

|---------|-----|-------|-------|------------|------------|------|

| Present |     | Next  |       | Conditions | MUX inputs |      |

| State   |     | State |       |            |            |      |

| G1      | G0  | G1    | G0    |            | MUX1       | MUX2 |

| 0       | 0   | 0     | 0     | S'         |            |      |

| 0       | 0   | 0     | 1     | S          | 0          | S    |

| 0       | 1   | 0     | 0     | Z          |            |      |

| 0       | 1   | 1     | 0     | Z'         | Z'         | 0    |

| 1       | 0   | 1     | 1     |            | 1          | 1    |

| 1       | 1   | 1     | 0     | E'         |            |      |

| 1       | 1   | 0     | 1     | E          | E'         | Е    |

|         |     |       |       |            |            |      |