#### Chapter 5

Synchronous Sequential Logic

Chapter 5

#### Introduction

- Circuits require memory to store intermediate data

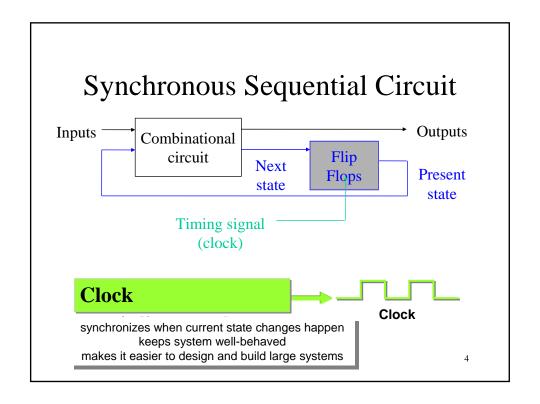

- Sequential circuits use a periodic signal to determine when to store values.

- A clock signal can determine storage times

- Clock signals are periodic

- Single bit storage element is a flip flop

- A basic type of flip flop is a atch

- Latches are made from logic gates

- NAND, NOR, AND, OR, Inverter

Chapter 5

#### Synchronous vs. Asynchronous

- Synchronous sequential circuit is a system whose behavior can be defined from the knowledge of its signal at discrete instants of time

- Asynchronous sequential circuit is a system whose behavior can be defined from the knowledge of its signals at any point of time

Chapter 5

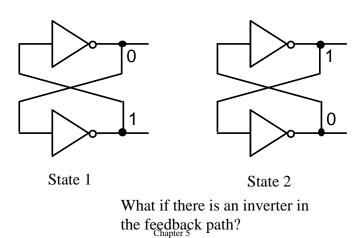

#### **Cross Coupled Inverters**

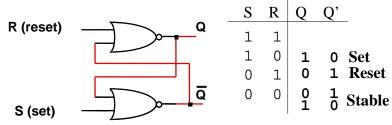

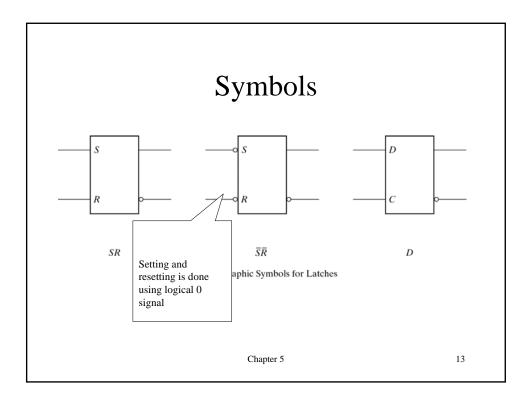

#### SR Latch using NOR

°S-R latch made from cross-coupled NORs

°If Q = 1, set state

°If Q = 0, reset state

°Usually S=0 and R=0

°S=1 and R=1 generates unpredictable results

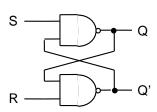

# SR latch using NAND

| Q'                                      |

|-----------------------------------------|

| 1 Disallowed                            |

| 0 Set                                   |

| <ul><li>0 Set</li><li>1 Reset</li></ul> |

| <sup>1</sup> Store                      |

|                                         |

- Latch made from cross-coupled NANDs

- Sometimes called S'-R' latch

- Usually S=1 and R=1

- S=0 and R=0 generates unpredictable results

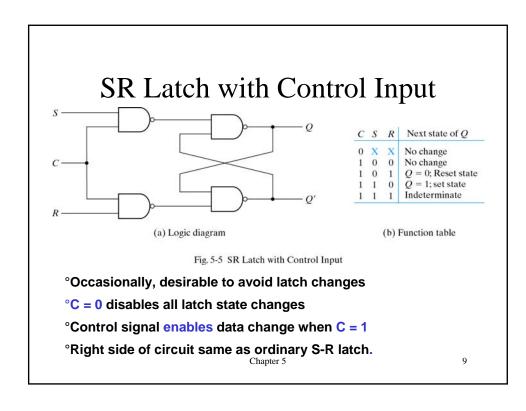

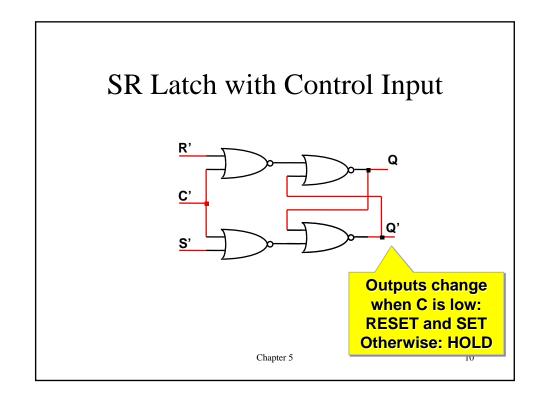

SR Latch R (Reset)  $RQ\overline{Q}$ Set state Reset state Undefined S (Set) (a) Logic diagram (b) Function table S (Set) Set state Reset state Undefined R (Reset) (b) Function table (a) Logic diagram Chapter 5 8

#### D Latch

Chapter 5

11

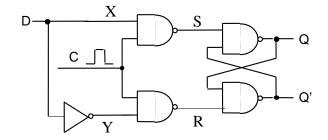

#### D Latch

- One wat to avoid the indeterminate state in the SR latch when both S and R are This is done by inverting S and having the inverted S as R.

- As long as C=0, no change. If C=1 D is delivered to Q and D' to Q' C D Q Q'

0 X Q Q'

1 1 1 0

1 0 0 1

Chapter 5

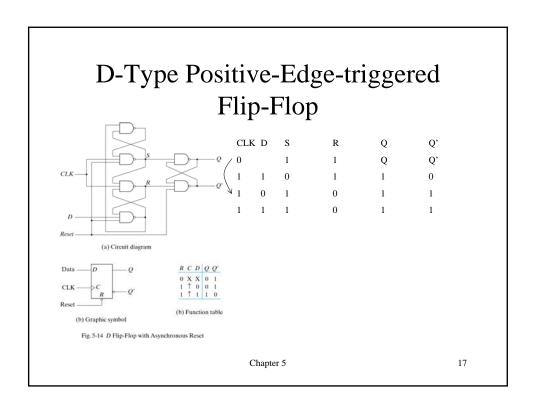

#### Flip-Flops

- The state of the latch or flip-flop is switched by a change in the control input, this is called a *trigger*

- The D latch with pulses in its control input. As long as the pulse input is 1, any changes in the D input is transferred to the output.

- When the state of the latch changes, if the control pulse is still at logic 1, any changes to the input (possible a feedback from the output) will change the output.

- Because of this, the output of a latch can not be applied directly to the input of this or other latches

#### Flip-Flop

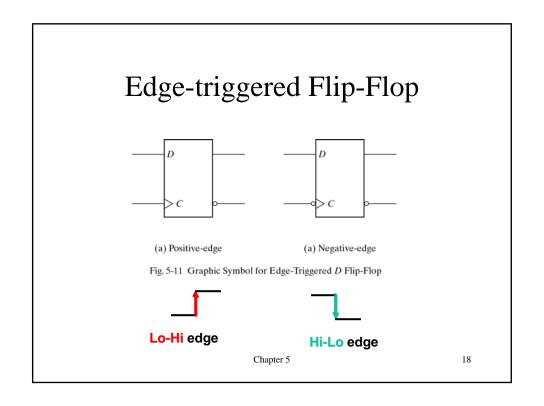

- A better way is if the flip-flop is triggered during the transition of the control input.

- A clock pulse goes through 2 transitions,  $1 \rightarrow 0$  and  $0 \rightarrow 1$ .

- The first is called –ve edge, the second is positive edge.

- There are two ways to implement this, either by using master-salve or by special design of the circuit.

Chapter 5

# Edge-Triggered Flip-Flop (Master-Slave) Do Do latch (master) CLK CLK

Fig. 5-9 Master-Slave D Flip-Flop

Any changes in the input can affect only Y as long as CLK=1; After CLK=0, Y propagates to Q, byt the master is locked.

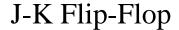

#### Characteristic Tables

• Characteristic tables Describes the operation of the flip-flop in a tabular form

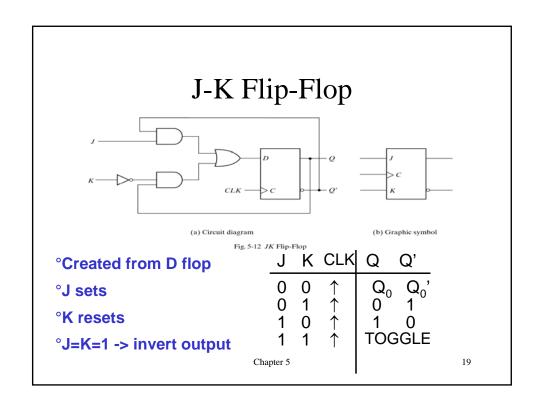

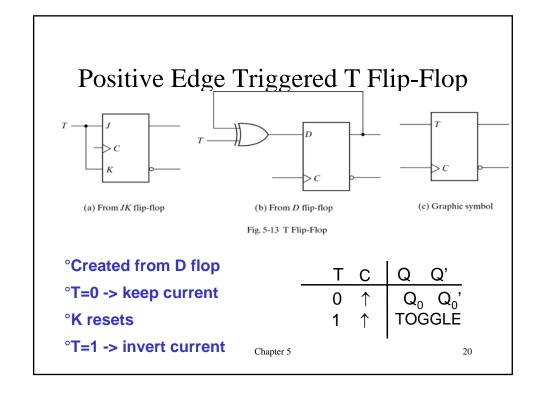

| JK Flip Flop |        | <b>D</b> Fl | ip Flop | F Fli | F Flip Flop |  |  |

|--------------|--------|-------------|---------|-------|-------------|--|--|

| J K          | Q(t+1) | D           | Q(t+1)  | T     | Q(t+1)      |  |  |

| 0 0          | Q(t)   | 0           | 0       | 0     | Q(t)        |  |  |

| 0 1          | 0      | 1           | 1       | 1     | Q'(t)       |  |  |

| 1 0          | 1      | ,           |         | '     |             |  |  |

| 1 1          | Q'(t)  |             |         |       |             |  |  |

Chapter 5

Characteristic Equation

• For D Flip-Flop

$$Q(t+1)=D$$

• For JK Flip-Flop

$$Q(t+1)=JQ'+K'Q$$

• For T Flip-Flop

$$Q(t+1)=T \oplus Q = TQ' + T'Q$$

Chapter 5

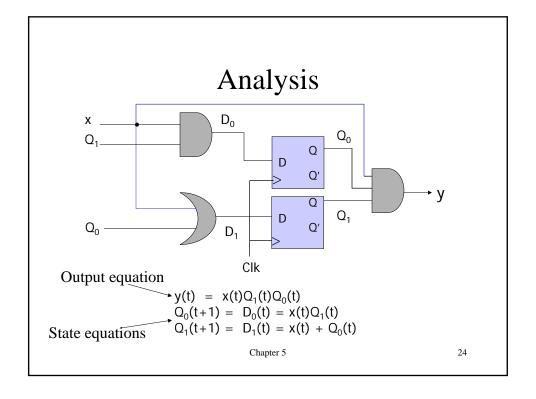

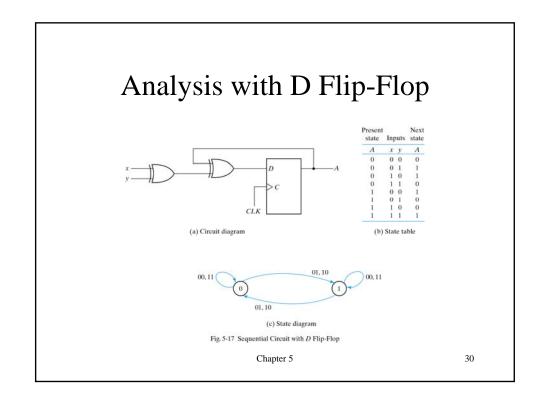

# Analysis of Clocked Sequential Circuits

- State equation, state table

- State diagram: states are represented by circuits, transitions by arcs labeled I/O

- Flip-Flop Equations:

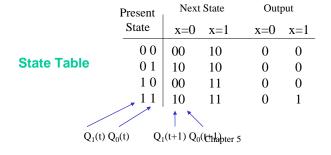

#### State Table

- Sequence of outputs, inputs, and flip flop states enumerated in state table

- Present state indicates current value of flip flops

- Next state indicates state after next rising clock edge

- Output is output value on current clock edge

#### State Table

- All possible input combinations enumerated

- All possible state combinations enumerated

- Separate columns for each output value.

- Sometimes easier to designate a symbol for each state.

|            | Present        | Next  | State | Outp | out |

|------------|----------------|-------|-------|------|-----|

| Let:       | State          | x=0   | x=1   | x=0  | x=1 |

| $s_0 = 00$ | $s_0$          | $s_0$ | $s_2$ | 0    | 0   |

| $s_1 = 01$ | $\mathbf{s}_1$ | $s_2$ | $s_2$ | 0    | 0   |

| $s_2 = 10$ | $s_2$          | $s_0$ | $s_3$ | 0    | 0   |

| $s_3 = 11$ | $s_3$          | $s_2$ | $s_3$ | 0    | 1   |

Chapter 5

| Present | Next | State | Output |     |  |

|---------|------|-------|--------|-----|--|

| State   | x=0  | x=1   | x=0    | x=1 |  |

| 0.0     | 00   | 10    | 0      | 0   |  |

| 0.1     | 10   | 10    | 0      | 0   |  |

| 1 0     | 00   | 11    | 0      | 0   |  |

| 1 1     | 10   | 11    | 0      | 1   |  |

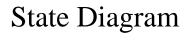

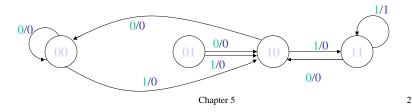

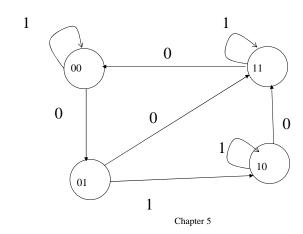

# State Diagram

- ° Each state has two arrows leaving

- $^{\circ}$  One for x = 0 and one for x = 1

- ° Unlimited arrows can enter a state

- ° Note use of state names in this example

- ° Easier to identify

Chapter 5

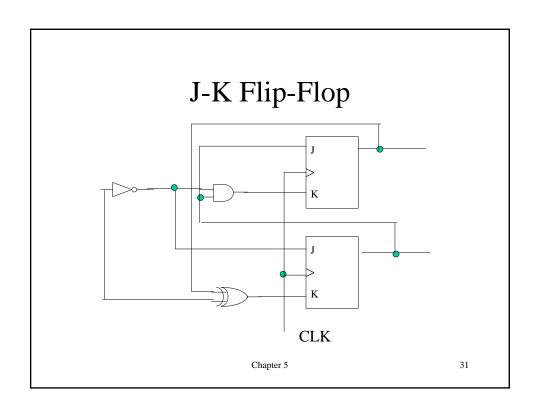

|         | J-K   | K Flip    | Flop |        |         |     |

|---------|-------|-----------|------|--------|---------|-----|

| Present | Input | Next      | F    | ip-Flo | p Inp   | uts |

| A B     | X     | A B       |      |        | $J_{B}$ |     |

| 0 0     | 0     | 0 1       | 0    | 0      | 1       | 0   |

| 0 0     | 1     | 0 0       | 0    | 0      | 0       | 1   |

| 0 1     | 0     | 1 1       | 1    | 1      | 1       | 0   |

| 0 1     | 1     | 1 0       | 1    | 0      | 0       | 1   |

| 1 0     | 0     | 1 1       | 0    | 0      | 1       | 1   |

| 1 0     | 1     | 1 0       | 0    | 0      | 0       | 0   |

| 1 1     | 0     | 0 0       | 1    | 1      | 1       | 1   |

| 1 1     | 1     | 1 1       | 1    | 0      | 0       | 0   |

|         |       | Chapter 5 |      |        |         | 32  |

33

#### Mealy and Moore Models

- Mealy model: the output is a function of both the present state and the input.

- Moore model: The output is a function of the present state only.

- In a Moore model, the output is synchronized with the clock (since it changes only if the state changes).

- In a Mealy model the output may change if the input changes during the clock cycle.

# **HDL** For Sequential Circuits

Chapter 5

# **Behavioral Modeling**

iitial

initial

begin

begin

clock=1'b0;

clock = 1'b0;

repeat(30)

#300 \$finish;

#10 clock = ~clock end; end always

#10 clock=~clock;

#### Behavioral Modeling

- One ways to use always statement always @ (A or B or reset)

- What fellows will be done if any changes in A, B, or reset,

- Or, we can use

Always @ (posedge clock or negedge reset)

Chapter 5

#### **Behavioral Modeling**

• Blocking assignment

B=A; C=B+1;

- A is assigned to B, and the new value is incremented

- Non-blocking assignment

B<=A; C<=B+1;

• Incrementing old value of A, because assignment is done after all the values in the block are done

#### Flip-Flops and Latches

```

//D Flip-Flop

//Description od D latch

\boldsymbol{module}\; D\_FF(Q,\,D,\,CLK);

module D_Latch (Q,D,control);

output Q;

output Q;

input D, CLK;

input D, control;

reg Q;

reg Q;

always @ (posedge CLK)

always @ (control or D)

Q=D;

if (control) Q=D;

endmodule

endmodule

```

Chapter 5 3

#### Flip-Flops and Latches

```

//D Flip-Flop with Asynchronous reset

module DFF(Q,D,CLK,RST);

output Q;

input D, CLK,RST;

reg

always @(posedge CLK or negedge RST);

if(~RST) Q=1'b0;

else Q=D;

endmodule

Only if RST=1 can posedge clock

event synchronously D->Q

Chapter 5

```

#### Other Types of Flip-Flop

```

// Flip-Flop (using D)

//JK Flip-Flop (using D)

Module TFF(Q,T,CLK,RST);

Module JKFF(Q,T,CLK,RST);

Output Q;

Output Q;

Input T,CLK,RST;

Input JK,CLK,RST;

Wire DT;

Wire JK;

Assign DT=Q^T;

Assign JK=(J\&\sim Q) \mid (\sim k\&Q);

DFF TF1(Q,DT,CLK,RST);

DFF JK1(Q,JK,CLK,RST);

endmodule

endmodule

Chapter 5

```

#### Other Types of Flip-Flop

```

//Functional Description of JK Flip-Flop

Module JK_FF(J,K,CLK,Q,Qnot);

output Q,Qnot;

input J,K,CLK;

reg Q;

assign Qnot=~Q

\verb"allways" @ (posedge CLK)"

case ({J,K})

2'b00: Q=Q;

2'b01: Q=1'b0;

2'b10: Q=1'b1;

2'b11: Q=~Q;

endcase

endmodule

Chapter 5

42

```

```

State Diagram

//Mealy state diagram

always @ (Prstate or x)

\boldsymbol{module}\; Mealy\_Model(x,y,CLK,RST);

case(Prstate)

input x,CLK,RST;

s0: y=0;

output y;

S1: if (x) y=1'b0; else y=1'b1;

reg y;

reg [1:0] Prstate, Nxtstate;

S2: if (x) y=1/b0; else y=1'b1;

S3: if (x) y=1'b0; else y=1'b1;

parameter S0=2'b00, s1=2'b01, s2=2'b10, S3=2'b11;

endcsde

always @ (posedge CLK or negedge RST)

endmodule

if(\sim RST) Prstate = S0;

else Prstate=Nxtstate;

always @ (Prstate or x)

case(Prstate)

S0: if(x) Nxtstate = S1;

else Nxtstate = S0;

S1: if (x) Nxtstate = S3;

else Nxtstate = S0;

S2: if (x) Nxtstate = S0;

\textbf{else}\ Nxtstate = S2;

S3: if(x) Nxtstate = S2;

else Nxtstate = S0;

endcase

Chapter 5

43

```

```

State Diagram

//Moore state diagram

module Mealy_Model(x,AB,CLK,RST);

input x,CLK,RST;

output [:0]AB;;

reg [1:0] State;

parameter S0=2'b00, s1=2'b01, s2=2'b10, S3=2'b11;

always @ (posedge CLK or negedge RST)

if(\sim RST) Prstate = S0;

else Prstate=Nxtstate;

always @ (Prstate or x)

case(Prstate)

S0: \mathbf{if}(\sim x) State = S1;

else State = S0;

S0: if (x) State = s2;

else State = S3;

S0: if (x) State = S3;

else State = S2;

S0: if(x) State = S0;

else State = S3;

endcase

assign AB=State;

Chapter 5

44

endmodule

```

#### Structural Description

#### Structural Description

```

//test fixture for the previous design

module testTFF;

reg x, CLK, RST;

wire y,A,B;

TCircuit (x,y,A,B,CLK,RST);

initial

begin

RST=0;

CLK=0;

#5 RST = 1;

repeat (16);

#5 CLK= ~CLK;

end

initial

begin

x=0;

#15 x=1;

repeat (8);

#10 x=~x

end;

endmodule

Chapter 5

46

```

#### State Reduction and Assignment

- In this part, we study some properties of the sequential circuits in order to reduce the number of gates or flip-flops.

- If we have *m* flip-flops, we can have up tp 2<sup>m</sup> states.

- Thus reducing the number of states, may result in reduction of the number of flip-flops.

- Sometimes, we care only about the output produced by a specific input sequence, while in others (counters) the states are important (considered as the output).

Chapter 5 47

#### State Reduction and Assignment

- There are infinite number of sequences that could be applied to the circuit, producing some output.

- B

- Two circuits (may have different states) will produce the same output for the same input are considered equivalent (from the input output point of view).

- We want to find a way to reduce the number of states and keeping the same input-output equivalence.

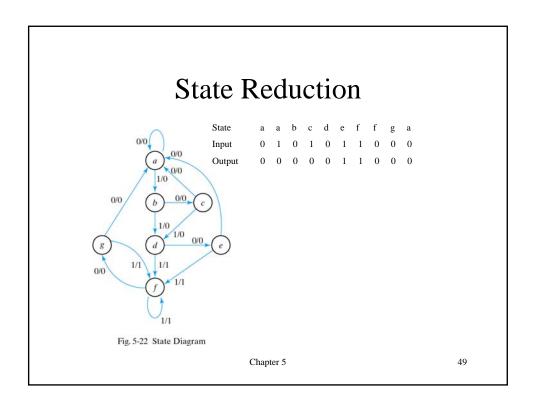

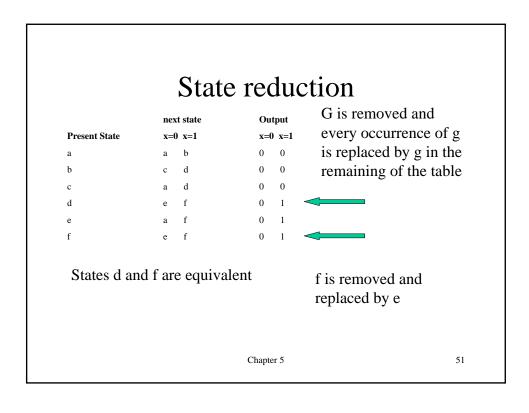

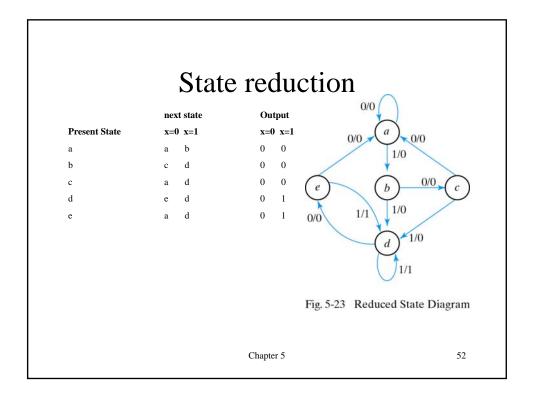

#### State reduction

|               | next | state | Outp | out |

|---------------|------|-------|------|-----|

| Present State | x=0  | x=1   | x=0  | x=1 |

| a             | a    | b     | 0    | 0   |

| b             | c    | d     | 0    | 0   |

| c             | a    | d     | 0    | 0   |

| d             | e    | f     | 0    | 1   |

| e             | a    | f     | 0    | 1   |

| f             | g    | f     | 0    | 1   |

| g             | a    | f     | 0    | 1   |

look for any two state that go to the same next state and have the same output for both input combination (states g and e), remove one and replace it by the other

#### State Assignment

- In this stage, you have to map states to binary numbers. You can use any mapping scheme.

- binary

- Gray code

- one-hot (more flip-flops)

Chapter 5 5

#### Design Procedure

- From the word description Derive the state diagram

- Reduce the number of states if necessary

- Assign Binary values to states.

- Obtain the binary-coded state table

- Choose the type of flip-flop

- Derive the simplified flip-flop input and output equations

- Draw the logic diagram

# Design

• Design a circuit that detects three or more consecutive ones.

# State table for sequence detector

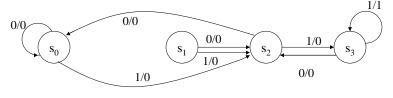

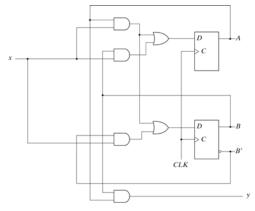

# Synthesis with D Flip-Flops

• Construct the state table

$$A(t+1) = D_{A}(A, B, X) = \sum_{ABX} (3,5,7)$$

$$B(t+1) = D_{B}(A, B, x) = \sum_{ABX} (1,5,7)$$

$$y(A, B, x) = \sum_{ABX} (6,7)$$

$$D_{A} = Ax + Bx$$

$$D_{B} = Ax + B'x$$

$$y = AB$$

Chapter 5

### Synthesis with D Flip-Flops

Fig. 5-26 Logic Diagram of Sequence Detector

Chapter 5

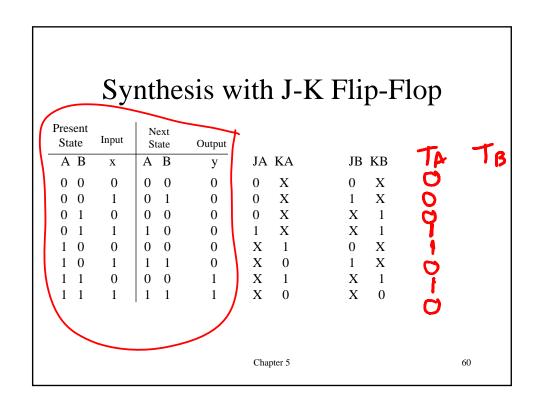

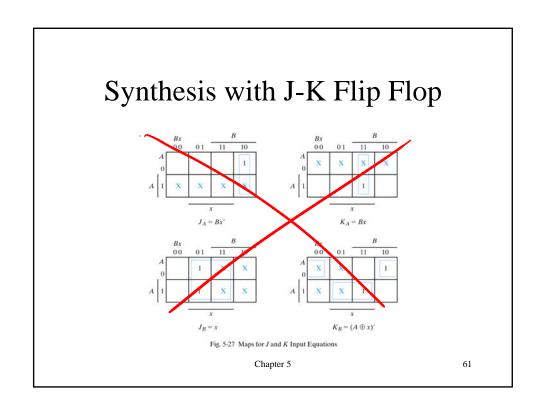

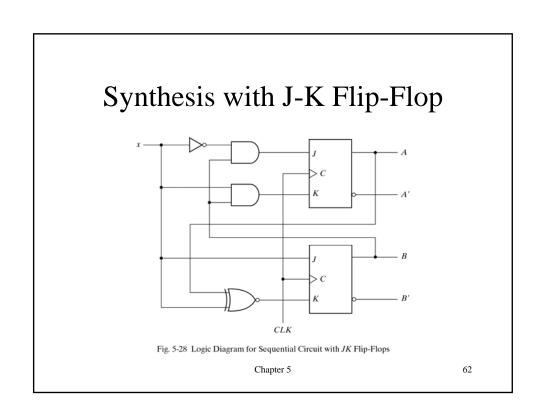

#### Synthesis with J-K Flip-Flop

• With J-K flip-flop, it is not as easy as D, since the output is not the same as the previous input, we need an excitation table

| Q(t) | Q(t+1) | J | K | Q(t)      | Q(t+1) | T |

|------|--------|---|---|-----------|--------|---|

| 0    | 0      | 0 | X | 0         | 0      | 0 |

| 0    | 1      | 1 | X | 0         | 1      | 1 |

| 1    | 0      | X | 1 | 1         | 0      | 1 |

| 1    | 1      | X | 0 | 1         | 1      | 0 |

|      |        |   | ( | Chapter 5 |        |   |

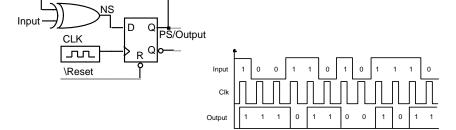

# Example: Odd Number of 1's

Assert output whenever input bit stream has odd # of 1's

| Present State | Input | Next State | Output |

|---------------|-------|------------|--------|

| 0             | 0     | 0          | 0      |

| 0             | 1     | 1          | 0      |

| 1             | 0     | 1          | 1      |

| 1             | 1     | 0          | 1      |

Note: Present state and output are the same value

Chapter 5

#### Odd Number of 1's

Example: Odd Parity Checker

**Next State/Output Functions**

NS = PS xor PI; OUT = PS

Chapter 5

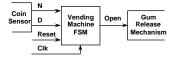

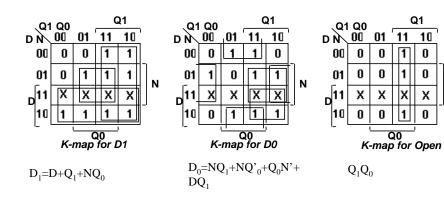

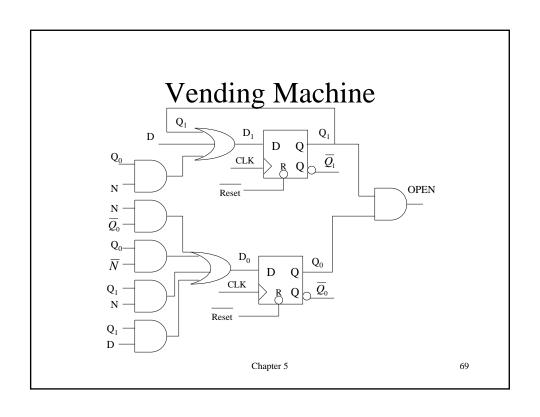

# Vending Machine

- □Deliver package of gum after 15 cents deposited

- □Single coin slot for dimes, nickels

- □No change

- □Design the FSM using combinational logic and flip flops

Chapter 5

65

Reuse states whenever possible

| Present<br>State | Inputs<br>D N | Next<br>State | Output<br>Open |

|------------------|---------------|---------------|----------------|

| 0¢               | 0 0           | 0¢            | 0              |

|                  | 0 1           | 5¢            | 0              |

|                  | 1 0           | 10¢           | 0              |

|                  | 1 1           | Х             | X              |

| 5¢               | 0 0           | 5¢            | 0              |

|                  | 0 1           | 10¢           | 0              |

|                  | 1 0           | 15¢           | 0              |

|                  | 1 1           | X             | X              |

| 10¢              | 0 0           | 10¢           | 0              |

|                  | 0 1           | 15¢           | 0              |

|                  | 1 0           | 15¢           | 0              |

|                  | 1 1           | X             | Χ              |

| 15¢              | ХХ            | 15¢           | 1              |

Symbolic State Table

Chapter 5

| Present State<br>Q <sub>1</sub> Q <sub>0</sub> | Inputs<br>D N | Next State<br>D <sub>1</sub> D <sub>0</sub> | Output<br>Open |

|------------------------------------------------|---------------|---------------------------------------------|----------------|

| 0 0                                            | 0 0           | 0 0                                         | 0              |

|                                                | 0 1           | 0 1                                         | 0              |

|                                                | 1 0           | 1 0                                         | 0              |

|                                                | 1 1           | X X                                         | X              |

| 0 1                                            | 0 0           | 0 1                                         | 0              |

|                                                | 0 1           | 1 0                                         | 0              |

|                                                | 1 0           | 1 1                                         | 0              |

|                                                | 1 1           | X X                                         | X              |

| 1 0                                            | 0 0           | 1 0                                         | 0              |

|                                                | 0 1           | 1 1                                         | 0              |

|                                                | 1 0           | 1 1                                         | 0              |

|                                                | 1 1           | X X                                         | X              |

| 1 1                                            | 0 0           | 1 1                                         | 1              |

|                                                | 0 1           | 1 1                                         | 1              |

|                                                | 1 0           | 1 1                                         | 1              |

|                                                | 1 1           | X X                                         | X              |

Chapter 5

Chapter 5

68

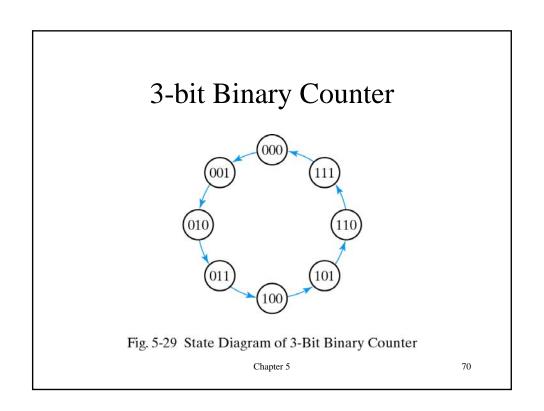

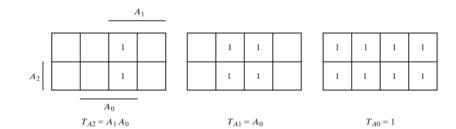

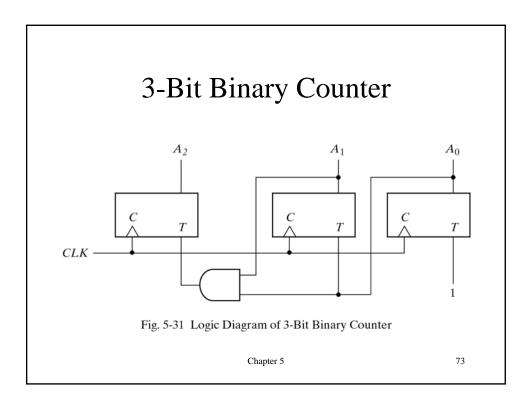

# 3-Bit Binary Counter

| Present State                                                                                               | Next State                                                                                                           | T-F Inputs                                           |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| A <sub>2</sub> A <sub>1</sub> A <sub>0</sub><br>0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 1 | A <sub>2</sub> A <sub>1</sub> A <sub>0</sub><br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0<br>1 1 1<br>0 0 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 1 1 1                                                                                                       | Chapter 5                                                                                                            | 1 1 1                                                |

# 3-Bit Binary Counter

Fig. 5-30 Maps for 3-Bit Binary Counter

Chapter 5 72

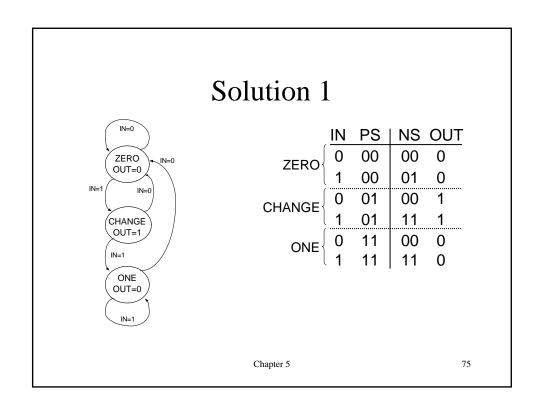

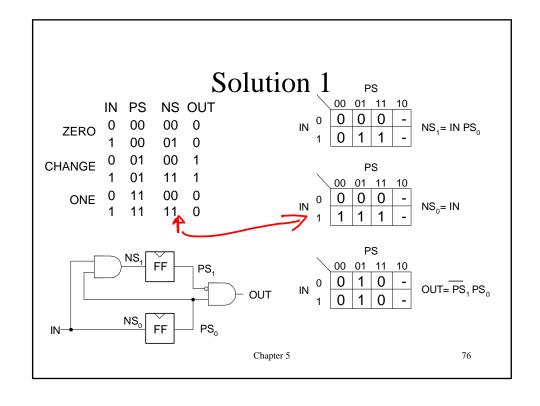

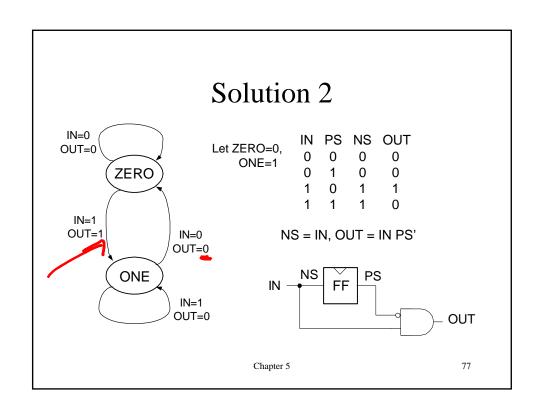

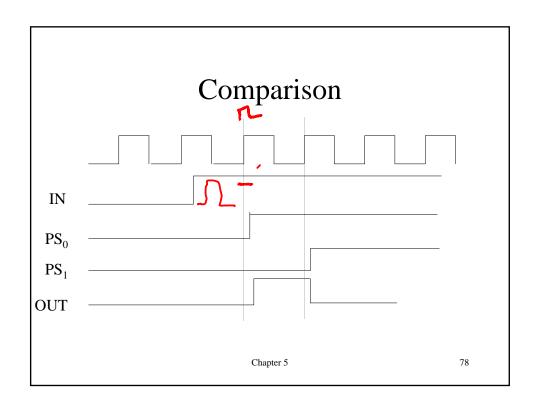

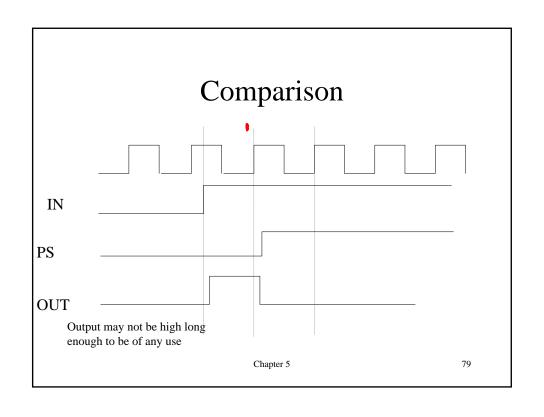

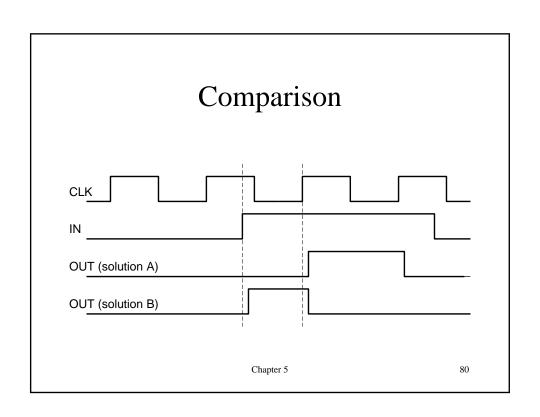

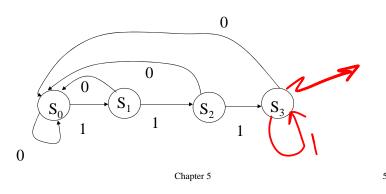

# Example (Mealy vs. Moore)

- Design a circuit that asserts its output for one cycle for every change in the input from 0 to 1

- We will try two different approaches.

- Compare between them