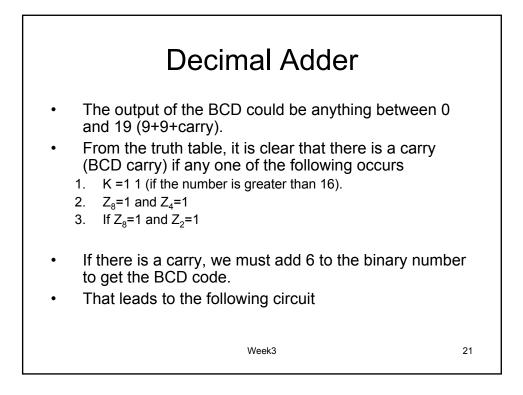

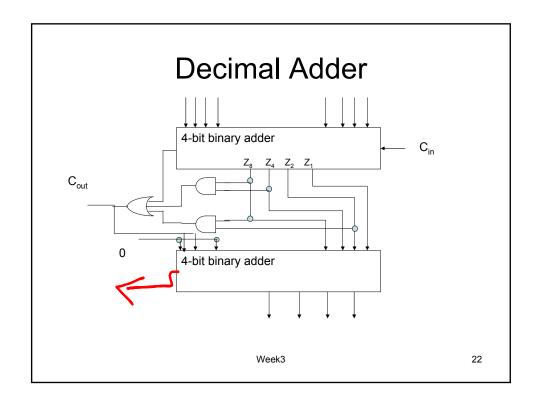

| Decimal Adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| Binary Sum         K       Z8       Z4       Z2       Z1         0       0       0       0       0         0       0       0       1       0         0       0       0       1       0         0       0       0       1       0         0       0       1       0       1         0       0       1       0       1         0       0       1       1       1         0       0       1       1       1         0       1       0       0       1         0       1       0       1       1         0       1       0       1       0         0       1       0       1       1         0       1       1       1       0         0       1       1       1       1         0       1       1       1       1         0       1       1       1       1         0       0       0       1       1         1       0       0       1       1 <th>BCD       Sum         K       Z8       Z4       Z2       Z1         0       0       0       0       0         0       0       0       0       1         0       0       0       1       0         0       0       0       1       1         0       0       1       0       0         0       0       1       1       0         0       0       1       1       1         0       0       1       1       1         0       0       1       1       1         0       1       0       0       1         1       0       0       1       1         1       0       0       1       1         1       0       0       1       1         1       0       1       0       1       1         1       0       1       1       1       1         1       0       1       1       1       1         1       0       1       1       1       1         1       &lt;</th> <th>Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19</th> <th></th> | BCD       Sum         K       Z8       Z4       Z2       Z1         0       0       0       0       0         0       0       0       0       1         0       0       0       1       0         0       0       0       1       1         0       0       1       0       0         0       0       1       1       0         0       0       1       1       1         0       0       1       1       1         0       0       1       1       1         0       1       0       0       1         1       0       0       1       1         1       0       0       1       1         1       0       0       1       1         1       0       1       0       1       1         1       0       1       1       1       1         1       0       1       1       1       1         1       0       1       1       1       1         1       < | Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |  |  |  |  |  |

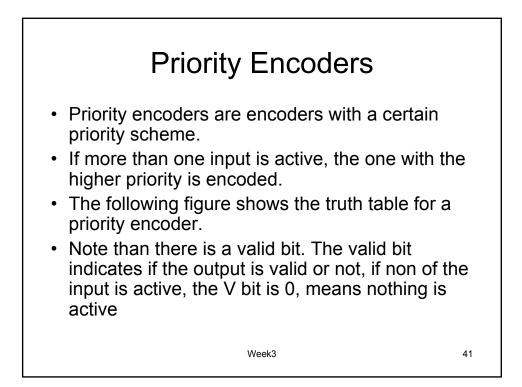

| What if mo                |                  |             |                | -   |                     |      | nas  | a val | lue of 1?                                             |  |

|---------------------------|------------------|-------------|----------------|-----|---------------------|------|------|-------|-------------------------------------------------------|--|

| Ignore "lo<br>Idle indica | tes th           | nat r       | no i           | npi | ut is               | a 1  |      |       | <b>T</b> . <b>L</b> . <b>(0</b> ) <b>M</b> . (        |  |

| Note that                 | <u>olari</u>     | <u>ty o</u> | ot Id          |     | <u>s or</u><br>outs | opos | site | trom  | <u>1 Table 4-</u> 8 in Mano<br>Outputs                |  |

|                           | I <sub>0</sub> I | [ 1 ]       | I <sub>2</sub> | I 3 | I 4                 | I 5  | I 6  | I 7   | $y_2 y_1 y_0$ Idle                                    |  |

|                           | 0                | 0           | 0              | 0   | 0                   | 0    | 0    | 0     | <b>x x x</b> 1                                        |  |

|                           | 1                | 0           | 0              | 0   | 0                   | 0    | 0    | 0     | 0 0 0 0                                               |  |

|                           |                  | -           | 0              |     | 0                   |      |      | 0     | 0 0 1 0                                               |  |

|                           |                  |             | 1              |     |                     | 0    |      | 0     | 0 1 0 0                                               |  |

|                           |                  |             |                | 1   |                     | 0    |      | 0     | 0 1 1 0                                               |  |

|                           |                  |             | X              | Х   | 1                   | 0    | 0    | 0     | 1 0 0 0                                               |  |

|                           |                  |             | X<br>X         | X   | X                   | 1    | 0    | 0     | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

|                           |                  |             | - X            | X   | X                   | X    | 1    | 0     | $1 \ 1 \ 0 \ 0$                                       |  |

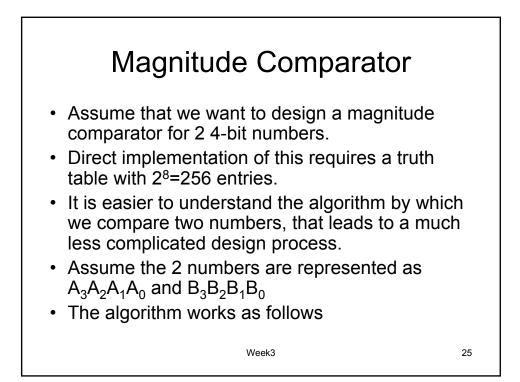

## Dataflow Modeling of a f-bit comparator potel magcomp (A,B,ALSB,AGTB,AEQB); input [3:0] A,B; dutput ALTB, AGTB,AEQB; assign ALTB = (A < B), AGTB = (A > B), dEQB = (A=B);

|  | Week3 | 70 |

|--|-------|----|

```

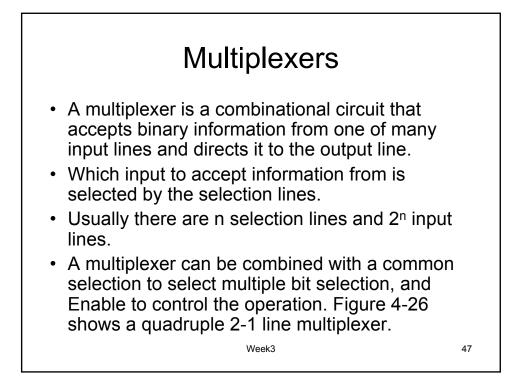

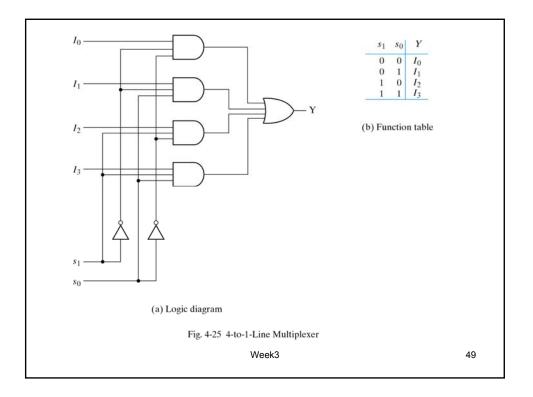

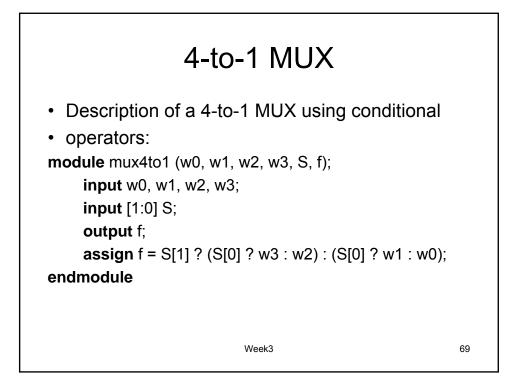

Description of a 4-to-1 MUX using a case statement:

module mux4to1 (W, S, f);

input [0:3] W;

input [1:0] S;

output f;

reg f;

always @(*)

case (S)

0: f = W[0];

1: f = W[1];

2: f = W[2];

3: f = W[3];

endcase

endmodule

Week3

71

```

```

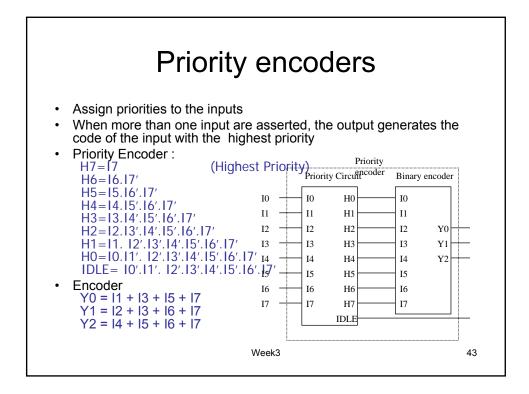

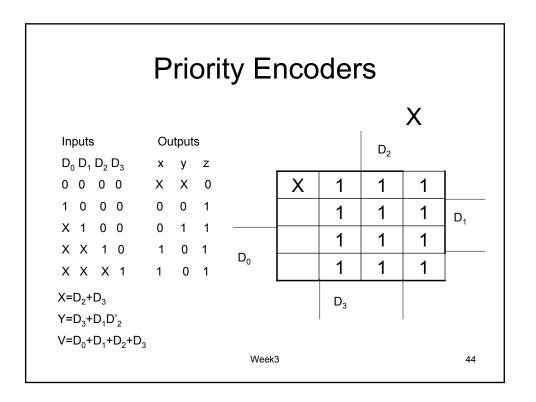

Verilog description of a priority encoder:

module priority (W, Y, z);

input [3:0] W;

output [1:0] Y;

output z;

reg [1:0] Y;

reg z;

always @(*)

begin

z = 1;

casex (W)

4'b1xxx: Y = 3;

4'b01xx: Y = 2;

4'b001x: Y = 1;

4'b0001: Y = 0;

default: begin

z = 0;

Y = 2'bxx;

end

endcase

end

endmodule

Week3

72

```

```

Verify description of a 16-to-1 MUX constructed as a tree off(t):module mux16to1 (W, S, f, M);input [0:15] W;input [0:15] W;input [3:0] R;output [3:0] M;mux4to1 Mux1 (W[0:3], S[1:0], M[0]);mux4to1 Mux2 (W[4:7], S[1:0], M[0]);mux4to1 Mux3 (W[8:11], S[1:0], M[2]);mux4to1 Mux4 (W[12:15], S[1:0], M[2]);mux4to1 Mux5 (M[0:3], S[3:2], f);

```