# Digital Logic Design

# Week 4 Combinational Design

Week3

### **Outline**

- · Combinational Circuits

- Analysis Procedure

- Design Procedure

- Adders and multipliers

- Comparators

- Decoders and Encoders

- Multiplexers

- · HDL For Combinational Circuits

#### **Combinational Circuits**

- What is a combinational circuit?

- What is the difference between combinational and sequential circuits

- Implementation MSI and standard cells in ASIC

Week3 3

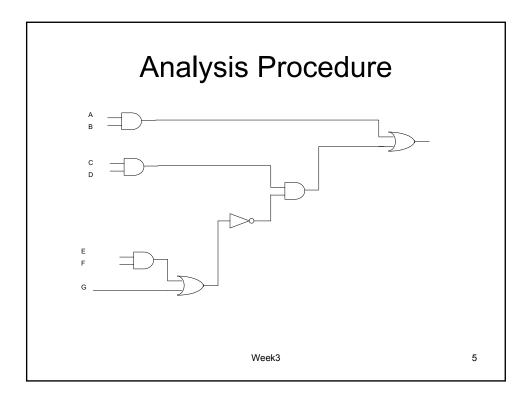

## **Analysis Procedure**

- Label all gate outputs that are a function of input variables with arbitrary symbols. Find the Boolean function of these gates

- Label all the gates that are functions of input variables and previously labeled gates with arbitrary symbols. Find the Boolean function of these gates.

- 3. Repeat step 3 until the outputs of all the gates are labeled

- 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables (or truth table)

# Design Procedure

- 1. From the specification of the circuit. Determine the required number of input and output and assign a symbol to each.

- 2. Derive the truth that defines the required relationship between inputs and outputs.

- 3. Obtain the simplified Boolean expressions for each output as a function of the input variables.

- 4. Draw the logic diagram and verify the correctness of the design.

- Example: BCD to Excess-3 Code Converter.

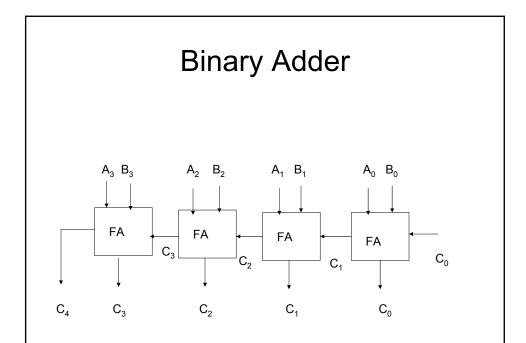

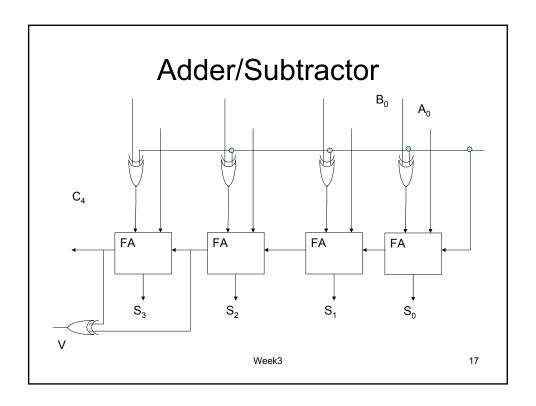

# Binary Adder-Subtractor

• Half adder: S=x'y+xy', C=xy

Week3

7

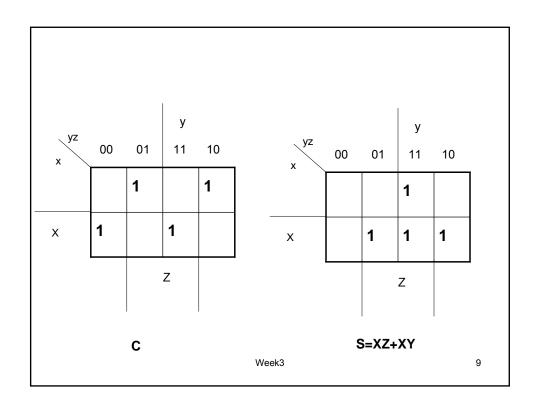

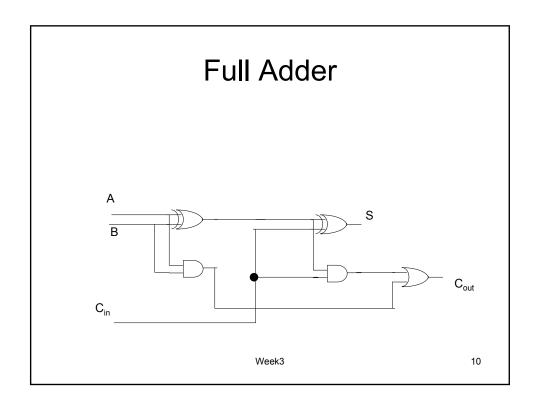

# Full Adder

| х | у | Z | s | С |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Week3

8

# **Carry Propagation**

Week3

- The value of s<sub>i</sub> depends on the current A<sub>i</sub> and Bi and C<sub>i</sub>. C<sub>i</sub> depends on A<sub>i-1</sub>, and B<sub>i-1</sub>, and so on.

- That means the carry propagates across all the digits in the two numbers to be added.

- Carry propagation time is a limiting factor on the speed of addition (basic operation in virtually everything).

- S<sub>i</sub>'s will not be ready at the same time

- · We need to speed-up addition

Week3 12

11

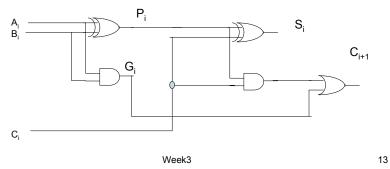

# **Carry Propagation**

$S_i {=} P_i \oplus C_i \qquad \qquad C_{i{+}1} {=} G_i {+} P_i C_i \quad \text{Carry if either } G_i \text{ or on of A,B and C}$

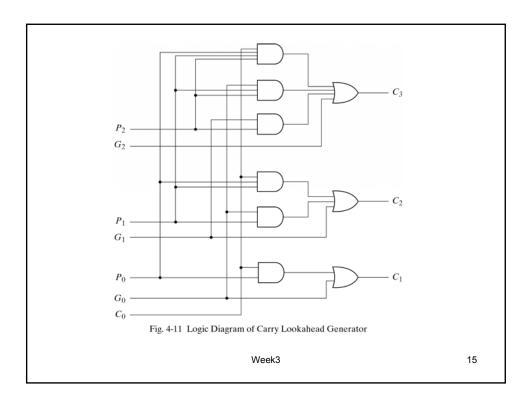

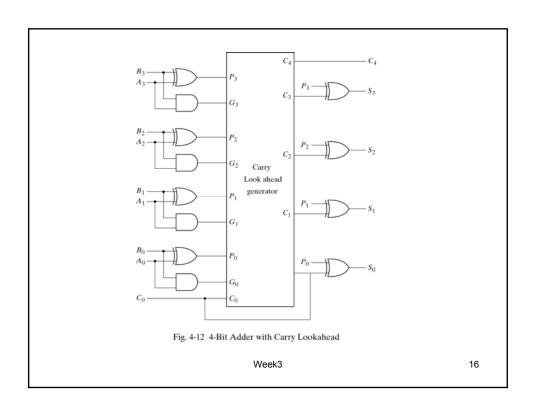

# Carry Lookahead

- G<sub>i</sub> is called the carry Generator, and P<sub>i</sub> is the carry propagate.

- We can calculate the carry at every stage by recursively substituting C<sub>i</sub>

C<sub>0</sub>=input carry

$C_1 = G_0 + P_0 C_0$

$C_2 = G_1 + P_1 C_1 = G_1 + P_1 G_0 + P_1 P_0 C_0$

$C_3 = G_2 + P_2C_2 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$

Circuit in Figure 4-11

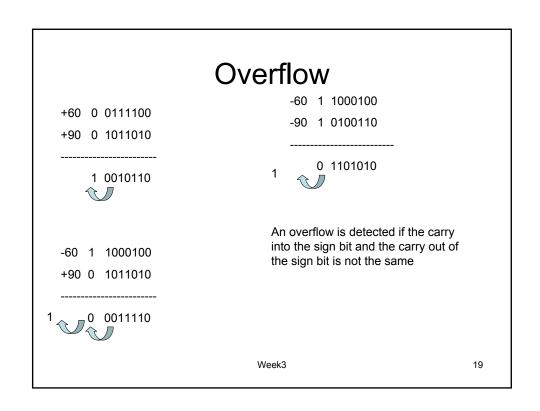

### Overflow

- When adding two n-bits number, the answer has a maximum of n+1 bits.

- If the numbers are represented in the computer by n bits, the n+1<sup>st</sup> bit is an overflow.

- Usually the overflow is detected and reported to the user.

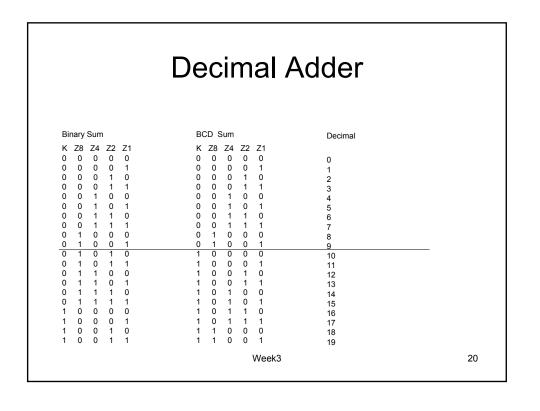

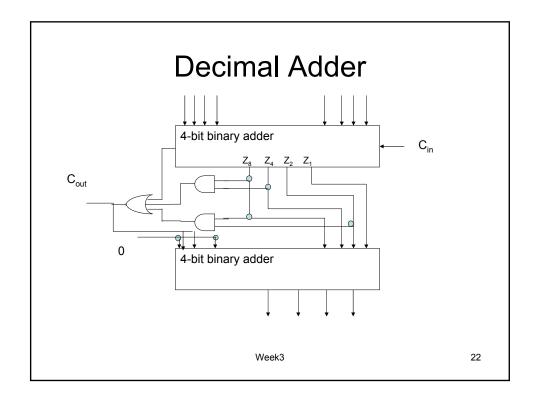

### **Decimal Adder**

- The output of the BCD could be anuthing between 0 and 19 (9+9+carry).

- From the truth table, it is clear that there is a carry (BCD carry) if any one of the following occurs

- 1. K =1 1 (if the number is greater than 16).

- 2.  $Z_8=1$  and  $Z_4=1$

- 3. If  $Z_8 = 1$  and  $Z_2 = 1$

- If there is a carry, we must add 6 to the binary number to get the BCD code.

- That leads to the following circuit

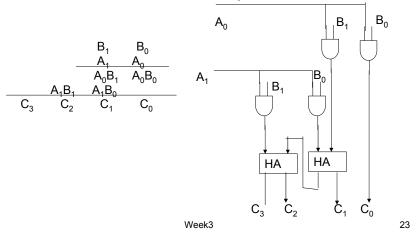

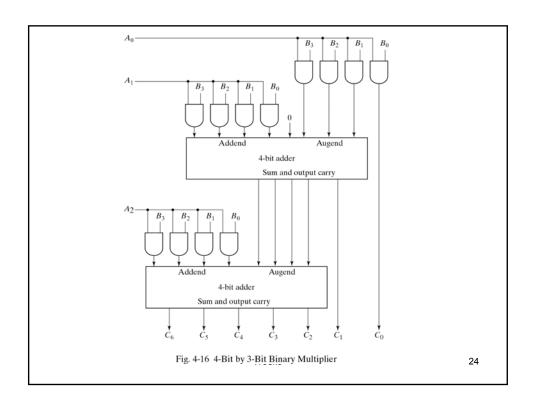

# **Binary Multiplier**

• First, consider 2 bit multiplier

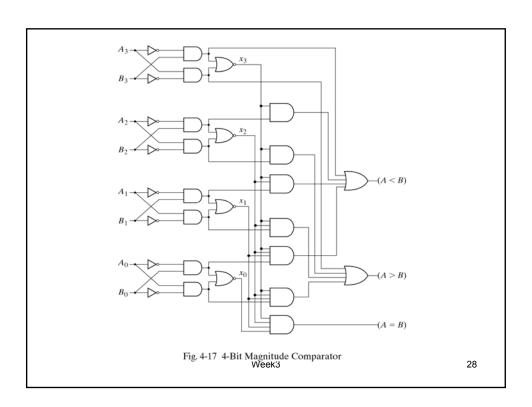

### Magnitude Comparator

- Assume that we want to design a magnitude comparator for 2 4-bit numbers.

- Direct implementation of this requires a truth table with 2<sup>8</sup>=256 entries.

- It is easier to understand the algorithm by which we compare two numbers, that leads to a much less complicated design process.

- Assume the 2 numbers are represented as A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub> and B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub>

- · The algorithm works as follows

Week3 25

### Magnitude Comparator

- The two numbers are equal iff all the bits in the 2 numbers are equal. That leads to a design of 4EX-OR followed by inverter (actually ex-nor) and an or gate.

- For A to be greater than B, we must have A<sub>i</sub> > B<sub>i</sub> and A<sub>i</sub>=B<sub>i</sub> j>i.

- So, we start at digit 3, compare A<sub>3</sub> and B<sub>3</sub>, either one is greater or they are equal we move to A<sub>2</sub> and B<sub>2</sub> and so on.

- If we define x<sub>i</sub> to be the ex-nor of A<sub>i</sub> and B<sub>i</sub> i.e. x<sub>i</sub> is 1 if A<sub>i</sub>=B<sub>i</sub>

# Magnitude Comparator

- · In this case,

- $(A=B)=x_3x_2x_1x_0$

- $(A>B)=A_3B_3'+x_3A_2B_2'+x_3x_2A_1B_1'+x_3x_2x_1A_0B_0'$

- (A>B) replace the prime from B to A.

- Circuit is shown in Figure 4-17

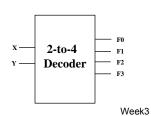

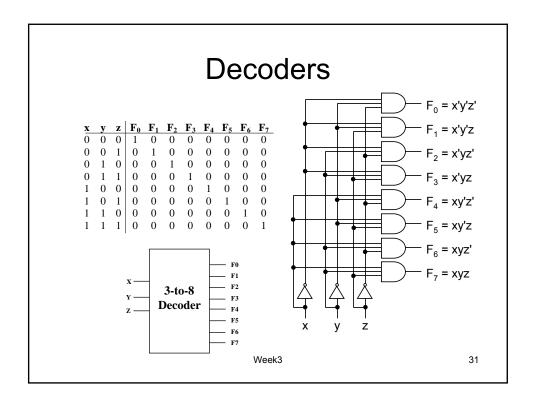

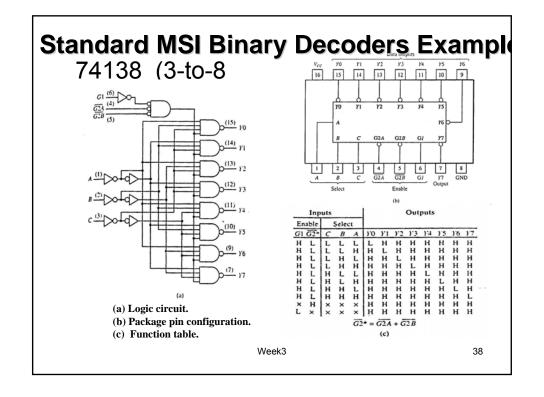

- A *decoder* is a combinational circuit that converts binary information from *n* inputs to a maximum of  $2^n$  outputs.

- A decode is called *n*-to-*m* decoder, where  $m \le 2^n$

- Consider 3-8 decoder, truth table with 3 inputs x,y,z and 8 outputs D<sub>7</sub> .. D<sub>0</sub> the circuit is shown in Figure 4-18

Week3 29

#### **Decoders**

| $\mathbf{X}$ | Y | $\mathbf{F_0}$ | $\mathbf{F_1}$ | $\mathbf{F}_2$ | $\mathbf{F}_3$ |  |

|--------------|---|----------------|----------------|----------------|----------------|--|

| 0            | 0 | 1<br>0<br>0    | 0              | 0              | 0              |  |

| 0            | 1 | 0              | 1              | 0              | 0              |  |

| 1            | 0 | 0              | 0              | 1              | 0              |  |

| 1            | 1 | 0              | 0              | 0              | 1              |  |

- From truth table, circuit for 2x4 decoder

is:

- Note: Each output is a 2-variable minterm (X'Y', X'Y, XY' or XY)

$F_0 = X'Y$   $F_1 = X'Y$   $F_2 = XY'$   $F_3 = XY$

30

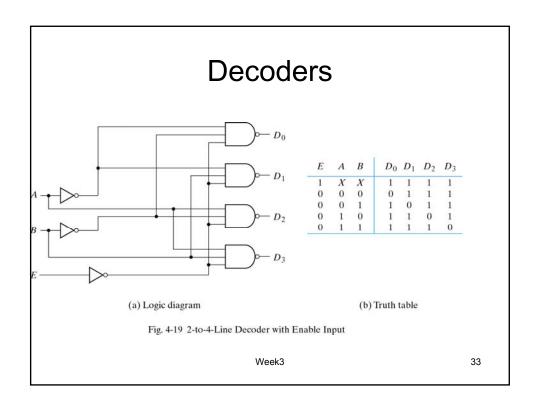

- Some decoders are implemented using NAND gates, in this case it will be more economical to produce the output in their complemented form.

- 2-4 decoder

- Circuit 4-19

- When E is 1, non

Of the outputs I 0

Decoder may be

Activated With E=0 or 1

| Ε | Α | В | $D_0$ | $D_1$            | $D_2$ | $D_3$ |

|---|---|---|-------|------------------|-------|-------|

| 1 | Χ | Χ | 1     | 1                | 1     | 1     |

| 0 | 0 | 0 | 0     | 1                | 1     | 1     |

| 0 | 0 | 1 | 1     | 0                | 1     | 1     |

| 0 | 1 | 0 | 1     | 1                | 0     | 1     |

| 0 | 1 | 1 | 1     | 1<br>1<br>0<br>1 | 1     | 0     |

|   |   |   |       |                  |       |       |

- A decoder with an Enable input can function as a demultiplexer

- A demultiplexer is a circuits that receives data from a single line, and direct it to a possible of 2<sup>n</sup> lines (example sharing a communication line).

- The decoder in the previous slide can function as a demultiplexer if we consider E to be the data and A, and B to be the input selection.

- Verify this by assuming selection 10 and determine the output (always equal to E).

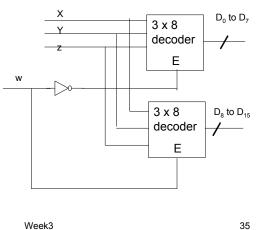

Decoders with enable can be connected together to form a larger decoder

#### **Decoders**

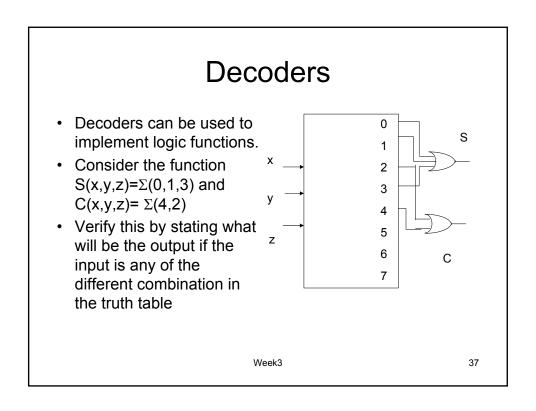

- Any n-variable logic function can be implemented using a single n-to-2<sup>n</sup> decoder to generate the minterms

- OR gate forms the sum.

- The output lines of the decoder corresponding to the minterms of the function are used as inputs to the or gate.

- Any combinational circuit with n inputs and m outputs can be implemented with an n-to-2<sup>n</sup> decoder with m OR gates.

- Suitable when a circuit has many outputs, and each output function is expressed with few minterms.

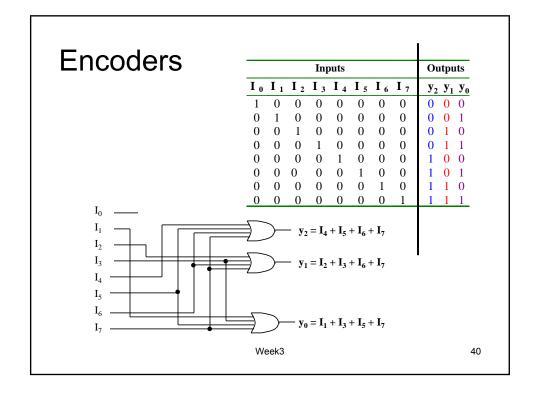

#### **Encoders**

- Encoders perform the reverse operation of a decoder.

- An encoder has up to 2<sup>n</sup> input lines, and n output lines.

- The encoder generates the binary code corresponding to the active input line.

- Truth table with 8 variables and three outputs, only need 1 in every row

- $x=D_1+D_3+D_5+D_7$ ;  $y=D_2+D_3+D_6+D_7$ ;  $Z=D_4+D_5+D_5+D_7$

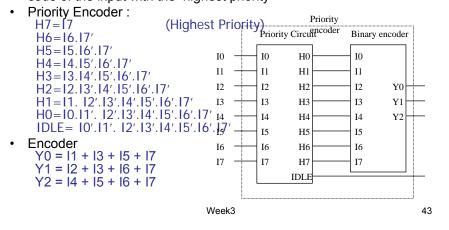

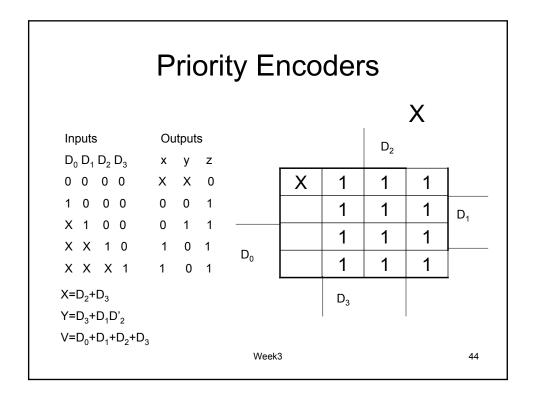

# **Priority Encoders**

- Priority encoders are encoders with a certain priority scheme.

- If more than one input is active, the one with the higher priority is encoded.

- The following figure shows the truth table for a priority encoder.

- Note than there is a valid bit. The valid bit indicates if the output is valid or not, if non of the input is active, the V bit is 0, means nothing is active

Week3 41

## **Priority Encoders**

- · What if more than one input line has a value of 1?

- Ignore "lower priority" inputs.

- Idle indicates that no input is a 1.

- Note that polarity of Idle is opposite from Table 4-8 in Mano

| Inputs         |                |                |     |     |     | Outputs |    |                |                       |                |      |

|----------------|----------------|----------------|-----|-----|-----|---------|----|----------------|-----------------------|----------------|------|

| I <sub>0</sub> | I <sub>1</sub> | I <sub>2</sub> | I 3 | I 4 | I 5 | I 6     | Ι, | $\mathbf{y}_2$ | <b>y</b> <sub>1</sub> | y <sub>0</sub> | Idle |

| 0              | 0              | 0              | 0   | 0   | 0   | 0       | 0  | X              | X                     | X              | 1    |

| 1              | 0              | 0              | 0   | 0   | 0   | 0       | 0  | 0              | 0                     | 0              | 0    |

| X              | 1              | 0              | 0   | 0   | 0   | 0       | 0  | 0              | 0                     | 1              | 0    |

| X              | X              | 1              | 0   | 0   | 0   | 0       | 0  | 0              | 1                     | 0              | 0    |

| X              | X              | X              | 1   | 0   | 0   | 0       | 0  | 0              | 1                     | 1              | 0    |

| X              | X              | X              |     | 1   | 0   | 0       | 0  | 1              | 0                     | 0              | 0    |

| X              | X              | X              | X   | X   | 1   | 0       | 0  | 1              | 0                     | 1              | 0    |

| X              | X              | X              | X   | X   | X   | 1       | 0  | 1              | 1                     | 0              | 0    |

| X              | X              | X              | X   | X   | X   | X       | 1  | 1              | 1                     | 1              | 0    |

# Priority encoders

- · Assign priorities to the inputs

- When more than one input are asserted, the output generates the code of the input with the highest priority

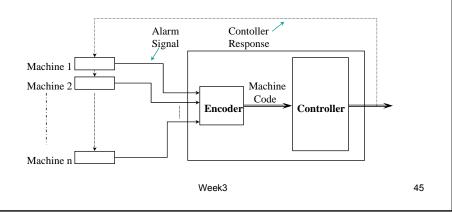

# **Priority Encoders**

- · Encoder identifies the requester and encodes the value

- · Controller accepts digital inputs.

## Summary

- Decoder allows for generation of a single binary output from an input binary code

- For an n-input binary decoder there are 2<sup>n</sup> outputs

- Decoders are widely used in storage devices (e.g. memories)

- We will discuss these in a few weeks

- Encoders all for data compression

- Priority encoders rank inputs and encode the highest priority input

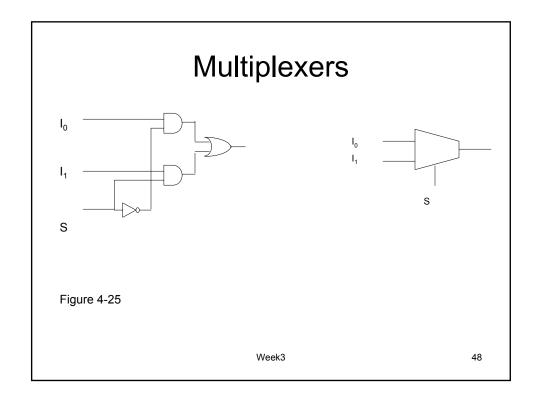

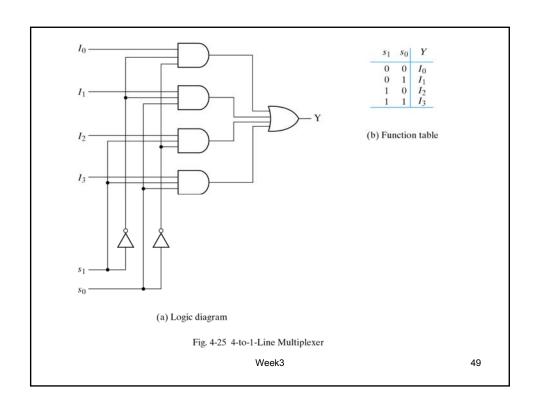

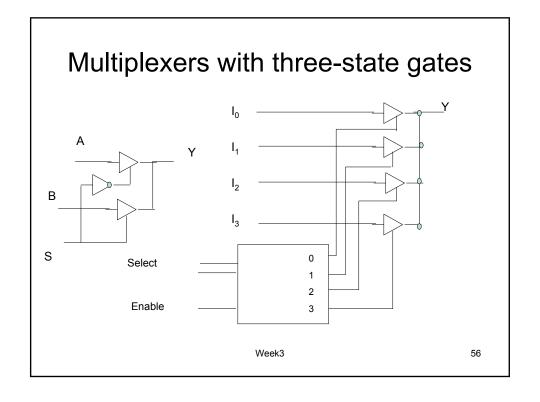

# Multiplexers

- A multiplexer is a combinational circuit that accepts binary information from one of many input lines and directs it to the output line.

- Which input to accept information from is selected by the selection lines.

- Usually there are n selection lines and 2<sup>n</sup> input lines.

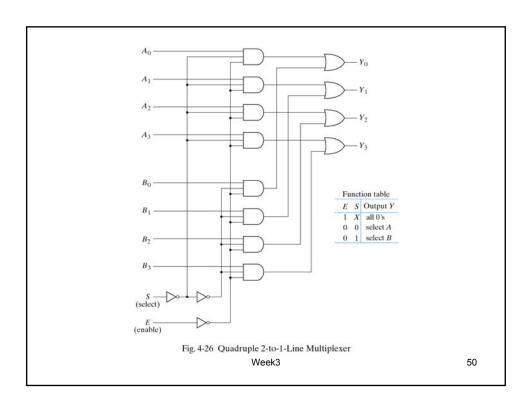

- A multiplexer can be combined with a common selection to select multiple bit selection, and Enable to control the operation. Figure 4-26 shows a quadruple 2-1 line multiplexer.

### **Function Implementation**

- We can consider the multiplexer to be a decoder that include the OR gates within.

- The OR minterms are generated by the function associated with the selection inputs.

- The rule to implement a function is as follows:

Week3 51

## **Function Implementation**

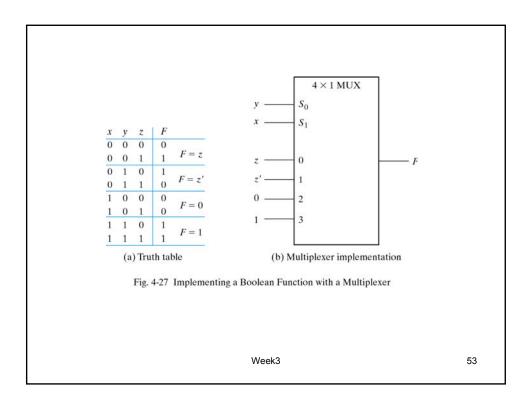

- Assume that we have n variables

- Choose n-1 of them to be the selection lines of a 2<sup>n-1</sup>-to-1 multiplexer.

- The selection lines chooses one of 2<sup>n-1</sup> inputs.

- These inputs corresponds to the truth table (2<sup>n</sup>) entries taken 2 entries at a time.

- Assume the n<sup>th</sup> variable is Z.

- These 2<sup>n-1</sup> entries each is Z, Z', 0, or 1

- According to the entry number, the corresponding input is one of these 4 values. 4-27 and 4-28

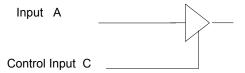

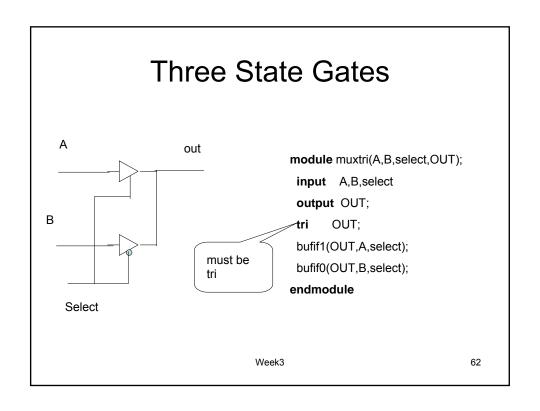

# Three States gates

The figure shows a three state buffer

$$Y = \begin{cases} Y = A & if C = 1 \\ Y = High Z & if C = 0 \end{cases}$$

#### **HDL** for Combinational Circuits

- A module in Verilog can be described in any one of the following modeling techniques

- Gate-level modeling using instantiation of primitive gates and user-defined modules.

- Dataflow modeling using continuous assignment statements with assign

- Behavioral modeling using procedural assignment statements with always

Week3 57

# Verilog (gate-level)

- In gate level we have the following primitive gates (and, nand, or, nor xor, xnor, not, buf)

- The system assigns four-valued logic to every gate (0,1,z,x).

- The truth tables for the 4 most used gates is shown in the next slide

# Verilog

```

and 0 1 x z

Or 0 1 x z

0 0 0 0

1 1 x x

0 1 x x

1 1 1 1

0 \times \times \times

x 1 x x

0 \times \times \times

x 1 x x

not Input output

xor 0 1 x z

0

1

0 1 0 0

0

1 0 x x

Х

x \times x \times x

x x x x

Week3

```

# Verilog 2-4 line decoder

```

//gate-level description of a 2-4 line decoder

module decoder_g1(A,B,E,D);

input

A,B,E;

output

[0:3]D;

wireAnot, Bnot, Enot;

not

n1(Anot,A),

n2(Bnot,B),

n3(Enot,E);

nand

n4(D[0],Anot,Bnot,Enot),

n4(D[1],Anot,B,Enot),

n4(D[2],A,Bnot,Enot),

n4(D[3],A,B,Enot);

endmodule

```

# **Dataflow Modeling**

Week3 63

# **Dataflow Modeling**

```

//Dataflow modeling of a 4-bit adder

module binary_adder (A,B,C_in,SUM,C_OUT);

input [3:0]A,B;

input C_in;

output [3:0] SUM;

output C_out;

assign {C_out,SUM} = A+B;

endmodule

```

# **Dataflow Modeling**

Week3 6

# **Dataflow Modeling**

```

//Dataflow model for a 2-to-1 mux

module mux2x1_df(A,B,select,OUT);

input A,B,select;

output OUT;

assign OUT= select? A : B;

endmodule

```

### behavioral description

```

//Behavioral description of a 2-1 line MUX module mux2_1 (A,B,select,OUT); input A,B,select; output OUT; reg OUT; always @ (select or A or B) if (select == 1) OUT = A; else OUT=b; endmodule

```

Week3 67

# Simulation (Test Bench)

- A test bench is a program for applying simulation to an HDL design.

- initial statements are executed at time 0

- always statements are executed always

- test module has no input or outputs

- The signals that are applied to the design module are declared as reg.

- The output of the design modules are declared as wire.

### 4-to-1 MUX

- Description of a 4-to-1 MUX using conditional

- operators:

```

\label{eq:module mux4to1} \begin{split} & \textbf{module } \ \text{mux4to1} \ (w0, \, w1, \, w2, \, w3, \, S, \, f); \\ & \textbf{input } \ w0, \, w1, \, w2, \, w3; \\ & \textbf{input } \ [1:0] \ S; \\ & \textbf{output } \ f; \\ & \textbf{assign } \ f = S[1] \ ? \ (S[0] \ ? \ w3: \, w2): (S[0] \ ? \ w1: \, w0); \\ & \textbf{endmodule} \end{split}

```

```

module mux4to1 (W, S, f);

input [0:3] W;

input [1:0] S;

output f;

reg f;

always @(*)

if (S == 0)

f = W[0];

else if (S == 1)

f = W[1];

else if (S == 2)

f = W[2];

else if (S == 3)

f = W[3];

endmodule

Week3

70

```

```

Description of a 4-to-1 MUX using a case statement:

module mux4to1 (W, S, f);

input [0:3] W;

input [1:0] S;

output f;

reg f;

always @(*)

case (S)

0: f = W[0];

1: f = W[1];

2: f = W[2];

3: f = W[3];

endcase

endmodule

Week3

71

```

```

Verilog description of a priority encoder:

module priority (W, Y, z);

input [3:0] W;

output [1:0] Y;

output z;

reg [1:0] Y;

reg z;

always @(*)

begin

z = 1;

casex (W)

4'b1xxx: Y = 3;

4'b01xx: Y = 2;

4'b001x: Y = 1;

4'b0001: Y = 0;

default: begin

z = 0;

Y = 2'bxx;

end

endcase

end

endmodule

Week3

72

```

```

Verilog description of a 16-to-1 MUX constructed as a tree of 4-to-1 decoders:

module mux16to1 (W, S, f, M);

input [0:15] W;

input [3:0] S;

output f;

output [3:0] M;

wire [0:3] M;

mux4to1 Mux1 (W[0:3], S[1:0], M[0]);

mux4to1 Mux2 (W[4:7], S[1:0], M[1]);

mux4to1 Mux3 (W[8:11], S[1:0], M[2]);

mux4to1 Mux4 (W[12:15], S[1:0], M[3]);

mux4to1 Mux5 (M[0:3], S[3:2], f);

endmodule

Week3

```