**CSE**

# CSE4210 Architecture and Hardware for DSP

Chapter 5

Unfolding

## **York University**

**CSE**

# Unfolding

- Unfolding is a transformation technique to change the program into another program such that one iteration in the new program describes more than one iteration in the original program.

- Unfolding, AKA loop unrolling in CSE4201.

- Unfolding factor of j means that one iteration in the new program describes j iterations in the old one.

**CSE**

# Unfolding

Also used to design bit parallel and word parallel architectures from bit serial and word serial architecture.

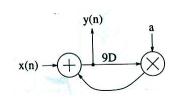

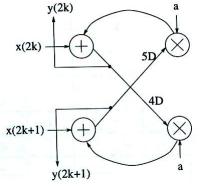

$$y(n) = ay(n-9) + x(n)$$

$$y(2k) = ay(2k-9) + x(2k)$$

$$y(2k+1) = ay(2k-8) + x(2k+1)$$

$$y(2k) = ay(2k-9) + x(2k)$$

$$= ay(2(k-5)+1) + x(2k)$$

$$y(2k+1) = ay(2k-8) + x(2k+1)$$

$$= ay(2(k-4)+0) + x(2k+1)$$

## York University

CSE

# unfolding

$$y(2k) = ay(2(k-5)+1) + x(2k)$$

$$y(2k+1) = ay(2(k-4)+0) + x(2k+1)$$

**CSE**

# Unfolding

- In the unfolded system, each delay is Jslow.

- That means if the input to a delay element is the signal x(kJ+m), the output is x((k-1)J+m) = x(kJ-J+m)

## **York University**

CSE

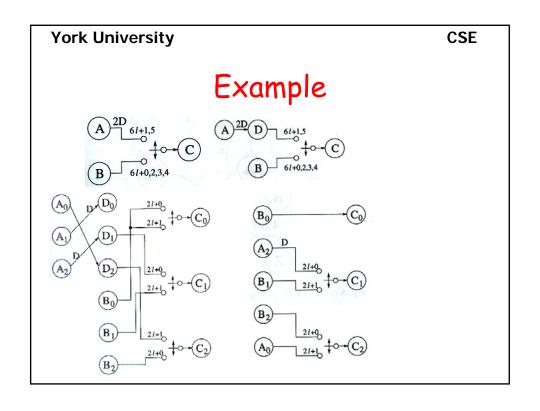

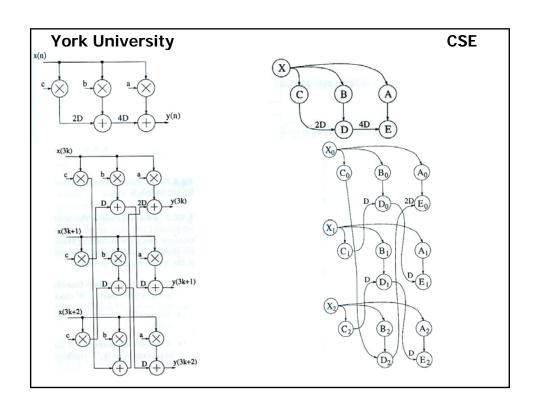

# Algorithm for Unfolding

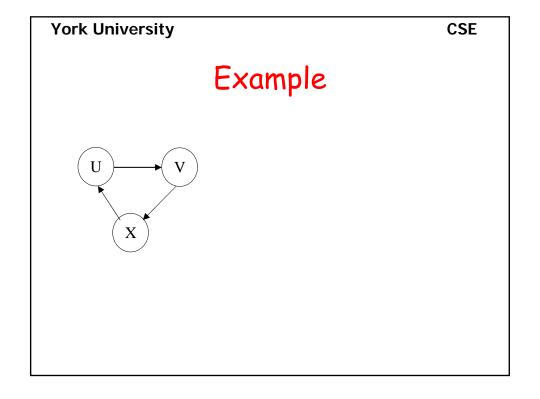

- For each node U in the original DFG, draw the J nodes  $U_0$ ,  $U_1$ , ...  $U_{J-1}$

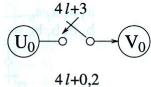

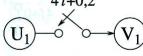

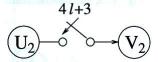

- For each edge U  $\rightarrow$  V with **w** delays in the original DFG, draw the **J** edges U<sub>i</sub>  $\rightarrow$  V<sub>(i+w)%J</sub> with  $\left|\frac{i+w}{J}\right|$  delays for i = 0,1,..,J-1

- For the input nodes, Ai corresponds to input signal x(jk+i)

- For J>w, an edge with w delays will result in J-w edges with zero delay and w edges with 1 delay

CSE

# Unfolding

Prove that the unfolded graph preserves dependence of the DSP program

## **York University**

**CSE**

# Properties

• Unfolding preserves the number of delays in a DFG  $\left| \frac{w}{J} \right| + \left| \frac{w+1}{J} \right| + ... + \left| \frac{w+J-1}{J} \right| = w$

**CSE**

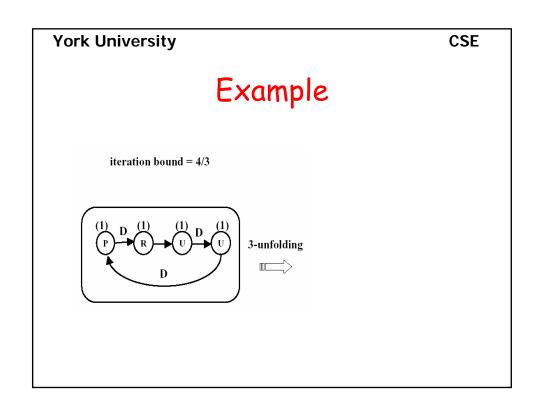

# Properties

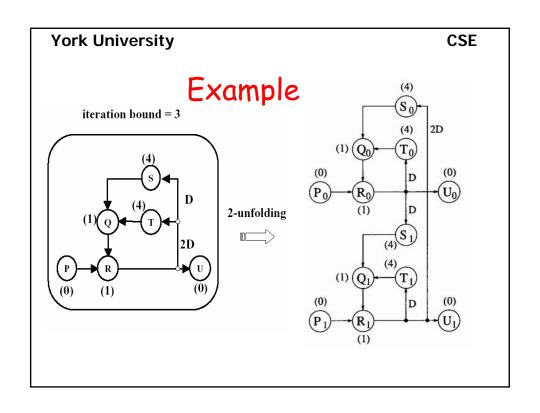

- **J**-unfolding of a loop with  $\mathbf{w}_{l}$  delays in the original DFG leads to

- $-\gcd(\mathbf{w}_{l},\mathbf{J})$  loops in the unfolded DFG

- each loop in J-unfolded DFG contains  $J/gcd(w_1, J)$  copies of each node that appears in loop /

- each loop in  ${f J}$ -unfolded DFG contains  $w_i$  /gcd( $w_i$  , ${f J}$ ) delays

## **York University**

**CSE**

## Properties

• Unfolding a DFG with iteration bound  $\textbf{T}_{\infty}$  results in

a J-unfolded DFG with iteration bound  $T_{\infty}$ ' =  $JT_{\infty}$

CSE

# Properties

- Property 5.4.1

- Consider a path with w delays in the original DFG.

J-unfolding of this path leads to (J-w) paths with no delays

and w path with 1 delay each, when w<J</li>

- Corollary 5.4.1

- Any path in the original DFG containing  ${\bf J}$  or more delays leads to  ${\bf J}$  paths with 1 or more delays in each path.

- A path in the original DFG with J or more delays cannot create a critical path in the J-unfolded DFG.

## York University

**CSE**

# Properties

- Any feasible clock cycle period that can be obtained by retiming the **J**-unfolded DFG,  $G_J$ , can be achieved by retiming the original DFG, G, directly and then unfolding it by unfolding factor **J**. i.e.  $(G_u)_r = (G_r)_u$

- Proof:

CSE

# **Applications**

- Unfolding can be used in

- Sample period reduction

- Parallel processing

## **York University**

**CSE**

# Sample Period Reduction

- Any implementation of a DSP program can never achieve an iteration period less than  $T_{\infty}$

- Some times we can not achieve that lower bound (2 reasons)

- When one node has a computation time greater than  $T_{\infty}$  (can not be split)

- $T_{\infty}$  is a fraction

CSE

# Word Level Parallel Processing

- · We start with a DSP at the word level

- We can use unfolding to replicate the design J times (J unfolding).

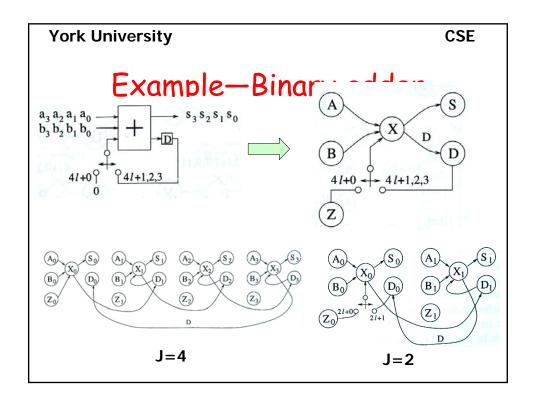

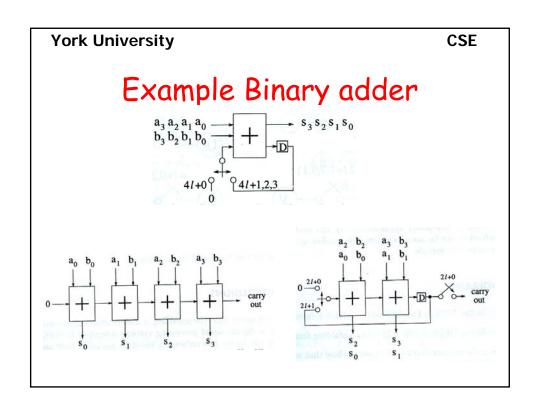

- Example

CSE

# Bit Level Parallel Processing

- Bit level parallel processing can increase the speed (reduce the sample time) be processing more than one bit at a time.

- Digit serial parallel processing is when we process W bits at a time where W is the word length.

- Usually involves switching (multiplexers)

## **York University**

CSE

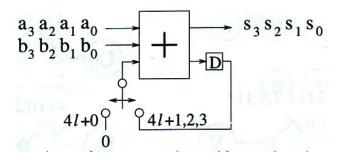

## Bit Serial Adder

Consider the following adder, W=4

**CSE**

# Edges with Switches

- Assumptions

- The word-length  ${\bf W}$  is a multiple of the unfolding factor  ${\bf J}$ , i.e.,  ${\bf W} = {\bf W}' {\bf J}$

- All edges into and out of the switches have no delays

- Write the switching instance as

$$Wl + u = J(W'l + \left| \frac{u}{J} \right|) + (u\%J)$$

• Step2: Draw an edge with no delays in the unfolded graph from the node  $U_{u\%J}$  to the node  $V_{u\%J}$ , which is switched at time instance  $(W'l + \left| \frac{u}{I} \right|)$ .

## York University

CSE

$$\begin{array}{c} 12 l+1,7,9,11 \\ \hline U & & V \end{array}$$

Example